### Accepted Manuscript

Low frequency noise investigation of n-MOSFET single cells for memory applications

E.G. Ioannidis, F.P. Leisenberger, H. Enichlmair

| PII:           | S0038-1101(18)30268-5                     |

|----------------|-------------------------------------------|

| DOI:           | https://doi.org/10.1016/j.sse.2018.10.016 |

| Reference:     | SSE 7484                                  |

| To appear in:  | Solid-State Electronics                   |

| Received Date: | 7 May 2018                                |

| Revised Date:  | 2 October 2018                            |

| Accepted Date: | 26 October 2018                           |

Please cite this article as: Ioannidis, E.G., Leisenberger, F.P., Enichlmair, H., Low frequency noise investigation of n-MOSFET single cells for memory applications, *Solid-State Electronics* (2018), doi: https://doi.org/10.1016/j.sse. 2018.10.016

This is a PDF file of an unedited manuscript that has been accepted for publication. As a service to our customers we are providing this early version of the manuscript. The manuscript will undergo copyediting, typesetting, and review of the resulting proof before it is published in its final form. Please note that during the production process errors may be discovered which could affect the content, and all legal disclaimers that apply to the journal pertain.

### Low frequency noise investigation of n-MOSFET single cells for memory

applications

E. G. Ioannidis, F. P. Leisenberger, H. Enichlmair.

Device and Process R&D, ams AG Tobelbader Strasse 30, 8141 Premstaetten, Austria

e-mail: E. G. Ioannidis: eleftherios.ioannidis@ams.com, F. P. Leisenberger:

friedrich.leisenberger@ams.com, H. Enichlmair: hubert.enichlmair@ams.com

#### Abstract

In this paper, we present a detailed investigation of low frequency noise (LFN) for different n-MOSFET devices dedicated for memory applications. We investigate the impact of the gate oxide thickness (GOX) on LFN. We analyzed how the position, the existence and the composition of Lightly Doped Dopant (LDD) implant in the source/drain region affect the LFN performance of the device. The results demonstrates that the thinner gate oxide and the device without LDD improved the noise performance compared the devices with thick GOX and with LDD implants. On the other hand, the absence of LDD implant on one side of the MOSFET didn't reveal a global trend for all measured devices. Finally, the different LDD implant composition resulted in different LFN performance which is gate area dependent. These results can be used from both process and design engineers to improve the LFN of n-MOSFET.

Keywords: low frequency noise, CMOS, n- MOSFET, logic NVM

C

#### **1. Introduction**

Today, it is well known that LFN can be used as a characterization tool for the quality and the reliability of the devices [1-2]. It is obvious that the level of noise has a direct impact on the device quality. In addition, LFN can influence the design of an electronic circuit since it can limit the overall performance and operation. Thus, the noise investigation of special architecture devices is of paramount importance for device and design engineers. Single transistors designed for logic NVM of SONOS type memory applications [3] can be used for LFN comprehension analysis due to the special architecture they have. In this experiment five single cell n-MOSFET devices were designed for memory applications and used for noise analysis.

In literature exists a number of publications referring to LFN characterization for logic NVM of SONOS type [4-7]. According to our knowledge, we could not find a prior work that used these type of devices for LFN improvement purposes and not for simple characterization. We tried not only to identify the main source of LFN in these devices but also to use this info for the improvement of LFN performance in CMOS technology.

In MOSFETs, it is generally accepted that the flicker (1/f-like) noise originates either from carrier number fluctuations (CNF) (Eques 1, 2 Table 1) [1] or from Hooge mobility fluctuations [8]. The CNF noise is due to carrier exchange between the near-interface gate dielectric traps and the channel. The charge fluctuations in the gate dielectric could also induce fluctuations of the carrier mobility, giving rise to the so-called correlated mobility fluctuations (CMF) (Eques 3, 4 Table 1)

[9-11].

These devices show great interest for 1/f noise analysis since they have special architecture in terms of LDD composition and gate oxide thickness. We are going to show how the different gate oxide thickness affects the noise performance when everything else in the device remains unchanged. We will see how the asymmetrical LDD implant or the lack of it (with/without LDD on Drain/Source side) can influence the LFN level. Finally, a comparison of two different LDD implants composition will give a better insight on the noise performance of the devices.

#### 2. Experiment

Electrical measurements were carried out on n- MOSFET transistors issued from a bulk CMOS technology node. The channel material is Si. Different width devices for L=0.18 $\mu$ m measured: W =0.22, 0.44, 2, 5 and 10 $\mu$ m. Different length devices for W=1 $\mu$ m measured: L=0.25, 0.3 and 0.4 $\mu$ m. The gate stack consists of SiON-based oxide dielectric with equivalent oxide thickness given in Table 2.

In the following, we are going to present the different measured devices in more details. We are going to use a prefix number i.e 1, 2, 3, 4 and 5 in order to distinguish them. Tables 2 and 3 summarizes the most important differences. It can be seen that these devices have a "special" architecture with or without or different LDD implants in the Source/Drain region and GOX thickness. These "exotic" devices can reveal useful insights of the LFN behavior of n-MOSFET. We can better understand how the gate oxide thickness affects the LFN when everything else remains unchanged (devices D1 and D2). We can investigate how the different LDD implant composition and the asymmetry of Source/Drain architecture affects the LFN with devices D2,

D3, D4 and D5.

Static characterization was performed in order to obtain the transfer (ID - VG) characteristics and then to extract typical MOSFET parameters. LFN measurements where performed using a Cascade Edge system [12] for low frequency noise measurements. Drain current noise measurements were carried out in linear region of operation. The drain voltage VD was fixed to 0.1V and the gate voltage varied from weak to strong inversion. The experimental bandwidth is 1Hz to 10KHz. It should be noted that all the spectra presented in this work are the average of at least 10 dies, thus suppressing the impact of Random Telegraph Signal (RTS)-induced Lorentzian-like spectra in small area devices [13]. All noise parameters were extracted at f=10Hz.

Below we will describe the analysis procedure we followed. First, we analyzed the basic DC operation of the devices to verify any abnormalities. It is not the purpose of this paper the in-depth investigation of the DC performance. Then, we focused on the noise measurements and specifically we used the average noise spectrum for the analysis. It had  $1/f^{\gamma}$  shape with  $\gamma$  close to unity. We investigated which model better fits our experimental data. Then, we used the basic extracted parameter from this model to compare the noise performance.

This paper focus on the understanding of how the different architecture devices affects the LFN performance. Thus, we compared devices with special features in order to analyze how this affect the noise performance. We investigated the impact of (i) gate oxide thickness (devices D1 and D2) (ii) devices with and without LDD on Drain/Source side (devices D2 and D4) (iii) LDD asymmetry on Drain side (devices D2 and D3) (iv) LDD asymmetry on source side (devices D3

and D4) and (v) different LDD implant composition on Drain side (devices D2 and D5) on LFN. In addition, we analyzed the impact of both gate device width and length by measuring devices with  $L=0.18\mu m$  and various widths and devices with  $W=1\mu m$  and various gate lengths.

#### 3. Results and discussion

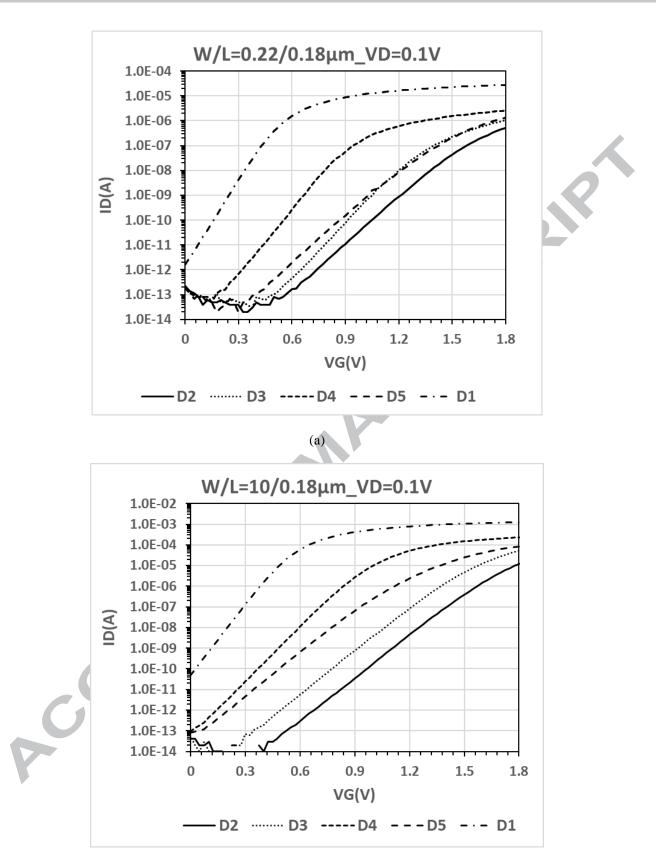

Fig. 1 shows simple IDVG curves for different width and length devices. These transistors are showing different DC performance since their basic process features are not the same i.e. different gate oxide thickness and LDD composition. Nevertheless, the devices are working properly and they are not showing any abnormalities.

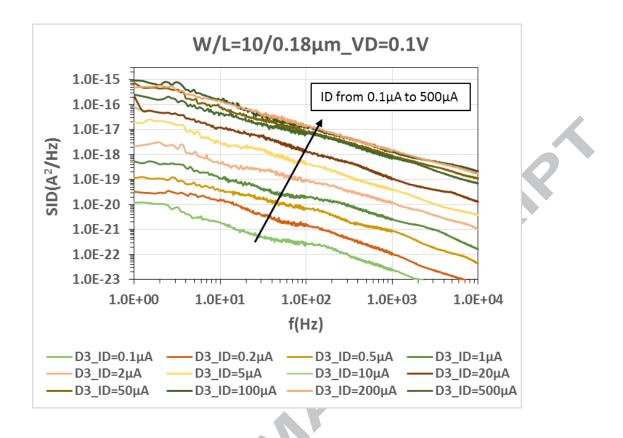

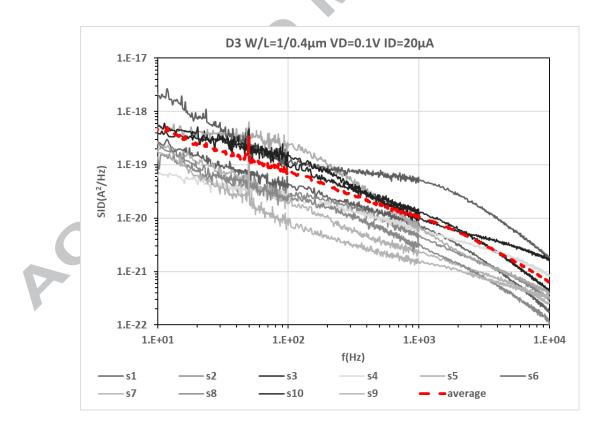

The drain current spectra of randomly selected devices are shown in Fig. 2 and various values of drain current. It is clear that the average noise spectra is  $1/f^{\gamma}$  like between 10 to 100Hz with  $\gamma$  close to 1. Similar results were obtained for all investigated bias conditions and devices. Fig. 3 shows the drain current spectrum for D3 W/L=1/0.4µm for ID=50µA and 10 sites. It can be seen from this graph the LFN dispersion. The average spectrum is showing 1/f-like shape.

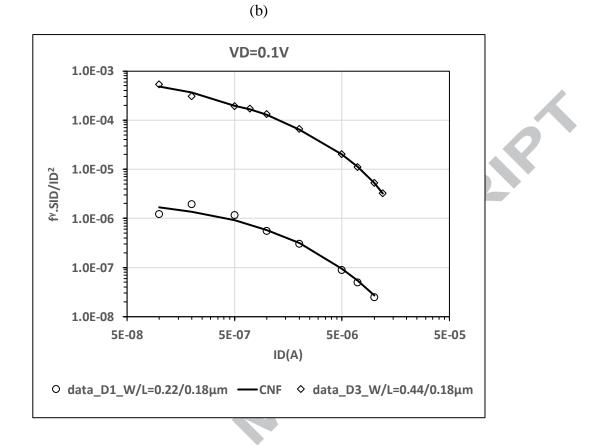

In order to verify which model better fits our experimental data we plotted the normalized drain current noise versus drain current in Fig. 4 for different area devices. The CNF model better describes our experimental data in all cases. According to this model, see Equ. 1-2 Table 1, the flat band voltage spectral density, SVFB, is the main parameter and the one we will use to compare the LFN performance. This parameter of each measured area and type of device is extracted according Equ. (1) and it is used for the comparison of the LFN performance.

According to [14], we used the statistical mean values of the linear noise data. The linear data

mean values are nearly constant with the device area, indicating that the quality of the gate oxide is maintained even at very small device area, showing no specific process-induced short or narrow channel effects.

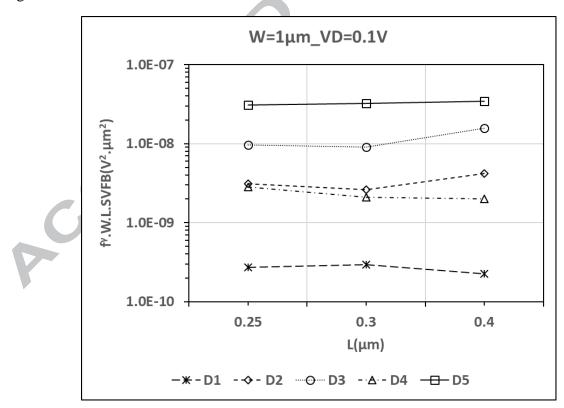

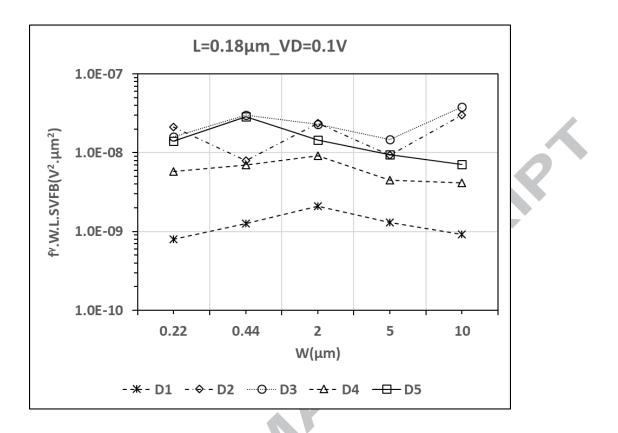

The next step in our analysis procedure is the comparison of the extracted normalized SVFB values from all devices. We tried to divide the analysis in different parts because we wanted to focus on the impact of specific device features on LFN. Figs 5 and 6 are showing the normalized flat band voltage spectral density versus device width and length for all measured devices, respectively.

• Impact of Gate Oxide thickness (Devices D1 and D2). In all cases D2 is showing much higher noise compared to D1. This is attributed to the different gate oxide thickness that affects the noise level according to Equ. (2). D2 has thicker gate oxide thus smaller equivalent gate oxide capacitance which leads to higher flat band voltage spectral density assuming that the volumetric trap density is remaining unaffected since we are talking about the same process.

• **Impact of LDD in both sides (Devices D2 and D4).** D4 does not have any LDD implant in both Source and Drain side. In all cases, the normalized flat band voltage spectral density of D4 is smaller compared to D2. There are many studies of the impact of LDD in LFN [14-17] and all of them concludes that the LDD is increasing the LFN through the raise of source/drain resistance. We verified this tendency for all measured devices.

• Impact of LDD in Drain side (Devices D2 and D3). For devices 2 and 3, we investigated how the LDD implant in Drain side can influence the LFN performance of the

devices. D2 has the LDD implant on both sides compared to D3 that it has it only in Source side. It can be seen that D3 has higher normalized flat band voltage spectral density values compared to D2 for all measured devices for W=1 $\mu$ m. The situation is not clear for devices with L=0.18 $\mu$ m. One could consider in this case that the lack of LDD in Drain side will directly lead to an improvement of LFN in all cases. Apparently there is a different trend for devices with different width and length. The asymmetry of drain/source side alters the LFN device performance in respect to the device width and length.

• Impact of LDD in Source side (Devices D3 and D4). In this case, the device D3 with LDD on source side has higher noise compared to the one with no LDD implant.

• Impact of different LDD composition in Drain side (Devices D2 and D5). Finally, the devices D2 and D5 which are having different LDD composition in Drain side showed the following results. D5 is showing higher noise than D2 for all different gate lengths and constant gate width but not in the other case. For L=0.18µm, it is unclear which device shows higher noise since it depends on the device gate width.

One possible explanation for the results concerning devices 2,3,4 and 5 could be found in a previous work regarding the impact of LDD implants on LFN, Ref. [15]. Based on this work we verified that the LDD composition can alter the carrier distribution for each device geometry differently. Thus, the noise performance can be different for each device width and length leading to different trend, which is verified from this study as well.

#### 4. Conclusions

In this manuscript, we investigated the LFN performance of special n-MOSFET transistors dedicated for logic NVM memory applications. The architecture of these devices can improve our understanding of the LFN behavior of n-MOSFET. Here we compared the impact of different gate oxide thickness on the LFN. The devices with thicker gate oxide thickness are nosier compared the thinner ones. Then, we investigated how the LDD implant on source/drain side can influence the noise level. The devices with no LDD in both sides are showing smaller noise. The analysis of the devices with LDD on drain/source side and with different LDD implant composition on drain side did not revealed a global trend. We have showed that the LFN of these devices is area dependent.

#### References

- [1] A. L. McWhorter, Semiconductor Surface Physics, H. Kingston, Ed. Philadelphia, PA, USA: Univ. Pennsylvania Press, 1957, p. 207.

- [2] C. Claeys and E. Simoen, "Noise as a diagnostic tool for semiconductor material and device characterization," J. Electrochem. Soc., vol. 145, no. 6, pp. 2058–2067, 1998.

- [3] Masatoshi Fukuda, Toshiro Nakanishi, Yasuo Nara, "Scaled 2bit/cell SONOS type Nonvolatile Memory Technology for Sub-90nm Embedded Application using SiN Sidewall Trapping Structure," IEEE International Electrons Device Meeting, pp. 37.5.1-37.5.4, 2003.

- [4] Tewook Bang, Byung-Hyun Lee, Choong-Ki Kim, Dae-Chul Ahn, Seung-Bae Jeon, Min-Ho Kang, Jae-Sub Oh, Yang-Kyu Choi, "Low-Frequency Noise Characteristics in SONOS Flash Memory With Vertically Stacked Nanowire FETs," IEEE Electron Device Letters, pp. 40-43, vol. 38, issue 1, 2017.

- [5] Hsin-Hui Hu, Yong-Ren Jheng, Yung-Chun Wu, Min-Feng Hung, Guo-Wei Huang, "Low-Frequency Noise in SONOS-TFT With a Trigate Nanowire Structure Under Program/Erase Operation," IEEE Electron Device Letters, pp. 1276-1278, vol. 33, issue 9, 2012.

- [6] Hsin-Hui Hu, Yong-Ren Jheng, Yung-Chun Wu, Min-Feng Hung, Guo-Wei Huang, "Low-Frequency Noise in Poly-Si TFT SONOS Memory With a Trigate Nanowire Structure," IEEE Electron Device Letters, pp. 1698-1700, vol. 32, issue 11, 2012.

- [7] Ui-Sik Jeong, Choong-Ki Kim, Hagyoul Bae, Dong-Il Moon, Tewook Bang, Ji-Min Choi,

Jae Hur, Yang-Kyu Choi, "Investigation of Low-Frequency Noise in Nonvolatile Memory Composed of a Gate- All-Around Junctionless Nanowire FET," IEEE Transactions on Electron Devices, pp. 2210-2213, vol. 63, issue 5, 2016.

- [8] F. N. Hooge, "1/ f noise is no surface effect," Phys. Lett., vol. 29, no. 3, pp. 139-140, 1969.

- [9] K. K. Hung, P. K. Ko, C. Hu, and Y. C. Cheng, "A unified model for the flicker noise in metal-oxide-semiconductor field-effect transistors," IEEE Trans. Electron Devices, vol. 37, no. 3, pp. 654–665, Mar. 1990.

- [10] G. Ghibaudo, O. Roux, C. Nguyen-Duc, F. Balestra, and J. Brini, "Improved analysis of low frequency noise in field-effect MOS transistors," Phys. Status Solidi A, vol. 124, no. 2, pp. 571–581, 1991.

- [11] E.G. Ioannidis, C.A. Dimitriadis, S. Haendler, R.A. Bianchi, J. Jomaah, G. Ghibaudo, "Improved analysis and modeling of low-frequency noise in nanoscale MOSFETs," Solid-State Electronics 76, pp. 54–59,2012.

- [12] <u>http://www.electronicsdatasheets.com/download/52cfe121e34e24cc6d56abd5.pdf?format=pdf</u>

- [13] C.G. Theodorou, E.G. Ioannidis, S. Haendler, E. Josse, C.A. Dimitriadis, G. Ghibaudo, "Low frequency noise variability in ultra-scaled FD-SOI n-MOSFETs: Dependence on gate bias, frequency and temperature", Solid-State Electronics, Volume 117, March 2016, Pages 88–93.

- [14] E.G. Ioannidis, C.G. Theodorou, S. Haendler, C.A. Dimitriadis and G. Ghibaudo, "Impact of low-frequency noise variability on statistical parameter extraction in ultra-scaled CMOS devices", ELECTRONICS LETTERS, 11th September 2014, Vol. 50, No. 19, pp. 1393–1395.

- [15] E.G. Ioannidis, K. Rohracher, F. Roger, W.C. Pflanzl, F.P. Leisenberger, E. Wachmann,

- E. Seebacher, V. Vescoli, "Impact of source/drain and bulk engineering on LFN performance of n- and p-MOSFET", Solid-State Electronics 135 (2017) 1–7.

- [16] E.P Vandamme, L.K.J Vandamme, C Claeys, E Simoen, R.J Schreutelkamp, "Impact of silicidation on the excess noise behavior of MOS transistors", Solid-State Electronics, pp. 1893-1897, volume: 38, Issue: 11, Nov. 1995.

- [17] XS Li, L.K.J Vandamme, "An explanation of 1/f noise in LDD MOSFETs from the ohmic region to saturation", Solid-State Electronics, pp. 1515-1521, volume: 36, Issue: 11, Nov. 1993.

- [18] XS Li, L.K.J Vandamme, "1/f noise in series resistance of LDD MOSTS", Solid-State Electronics, pp. 1471-1475, volume: 35, Issue: 10, Oct. 1992.

C

#### **Tables and Figures captions**

Table 1. CNF and CMF low frequency model.

- Table 2. LDD and GOX description

- Table 3. Measured devices

- Fig. 1. ID-VG curves for all type of devices for VD=0.1V with (a) W/L=0.22/0.18µm and (b)

W/L=10/0.18µm, respectively.

- Fig. 2. Drain current spectra for device D3 with  $W/L=10/0.18\mu m$  at VD=0.1V.

- Fig. 3. Drain current spectra of 10 sites for device D3 with W/L=1/0.4µm at VD=0.1V and

ID=50µA.

- Fig. 4. Normalized drain current spectral density versus drain current for VD=0.1V devices D1 with W/L=0.22/0.18µm and D3 with W/L=0.44/0.18µm.

- Fig. 5. Normalized flat band voltage spectral density for VD=0.1V and all device types versus various gate length for W=1 $\mu$ m.

- Fig. 6. Normalized flat band voltage spectral density for VD=0.1V and all device types versus various gate width for L=0.18 $\mu$ m.

#### Table 1. CNF and CMF low frequency model

$$CNF: \frac{SID}{ID^{2}} = (\frac{GM}{ID})^{2}.SVFB \quad (1)$$

$$CNF: SVFB = \frac{q^{2}.kT.\lambda.N_{t}}{W.L.C_{ox}^{2}.f^{\gamma}} \quad (2)$$

$$CMF: \sqrt{SVG} = \sqrt{SVFB} + \Omega.\sqrt{SVFB}.\frac{ID}{GM} \quad (3)$$

$$CMF: \frac{SID}{ID^{2}} = (\frac{GM}{ID})^{2}.SVFB.(1+\Omega.\frac{ID}{GM})^{2} \quad (4)$$

Where  $\Omega = a_{sc} \mu_{eff} C_{ox}$ ,  $a_{sc}$  is the Coulomb scattering coefficient,  $\mu_{eff}$  is the effective carrier mobility,  $C_{ox}$  is the gate dielectric capacitance per unit area, SVFB is the flat-band voltage spectral density,  $SVG=f^{\gamma}.SID/GM^2$  the input voltage spectral density, ID is the drain current, GM is the transconductance, SID is the drain current noise spectrum, kT is the thermal energy,  $\lambda$  is the tunnel attenuation distance ( $\approx 0.1$ nm for SiO<sub>2</sub>), q is the elementary charge, f is the frequency,  $\gamma$  is the slope of the drain current spectrum (close to 1) and N<sub>t</sub> is the gate dielectric trap density in cm<sup>-3</sup>.eV<sup>-1</sup>.

#### Table 2. LDD and GOX description

| Parameter | Description                                                 |

|-----------|-------------------------------------------------------------|

| LDD1      | B with X energy, Y dose and Z angle                         |

| LDD2      | As with higher energy than LDD1 and the same dose and angle |

| GOX1      | SiON-based oxide dielectric, EOT=4.45nm                     |

| GOX2      | SiON-based oxide dielectric, EOT=12.6nm                     |

### **Table 3. Measured devices**

| Device | Oxide type | LDD type |       |  |  |

|--------|------------|----------|-------|--|--|

|        |            | Source   | Drain |  |  |

| D1     | GOX1       | LDD1     | LDD1  |  |  |

| D2     | GOX2       | LDD1     | LDD1  |  |  |

| D3     | GOX2       | LDD1     | -     |  |  |

| D4     | GOX2       | -        | -     |  |  |

| D5     | GOX2       | LDD1     | LDD2  |  |  |

|        |            |          |       |  |  |

Fig. 1

Fig. 2

Fig. 4

**Dr. Eleftherios G. Ioannidis** was born in Kilkis, Greece. He received the B.Sc. degree in physics and the M.Sc. degree in electronic physics from the Aristotle University of Thessaloniki (AUTH), Thessaloniki, Greece, in 2006 and 2010, respectively. He received the Ph. D. degree in nanoelectronics from the AUTH and INPG in 2013. He is currently working with ams AG in Premstaetten, Austria. His current research interests include modeling and noise study in nanoscale device, reliability and electrical characterization and TCAD simulation.

MAN

Highlights: This paper investigates the impact on low frequency noise of n-MOSFET dedicated for memory applications. We analyze the impact of different gate oxide thickness and LDD composition in source/drain side on LFN performance. Accepter