معماری جدید شبکه بی سیم درون تراشه ای (WNoC) همراه با مسیرهای هدایت شده

چکیده

معماری های شبکه بی سیم درون تراشه ای (WNoC) به منظور بهبود عملکرد با کاهش تاخیر ارتباط هسته با هسته معرفی می شوند. شبکه های WNoC متداول پیام هایی را پخش می کنند که سبب افزایش ترافیک پهنای باند، تاخیر در ارتباط و مصرف توان می شود. مطالعات نشان می دهند که معماری ها مبتنی بر مسیردهی توان بالقوه ای در آدرس دهی همه پخشی پیام و بهبود عملکرد دارند. این کار یک معماری جدید شبکه های WNoC را همراه با مسیرهای توزیع شده (WNoC-DDs) پیشنهاد می دهد که از ارتباطات بی سیم به منظور ارتقاء اجرای سریع تر با کاهش تاخیر پشتیبانی می کند. بسته نرم افزاری VisualSim برای مدل سازی و شبیه سازی شبکه WNoC-DDs پیشنهادی، شبکه WNoC همراه با مسیر متمرکز (WNoC-CD) و یک مش دو بعدی متداول با پردازش سناریوهای مختلف ارتباطی مورد استفاده قرار می گیرد. معماری پیشنهاد به کاهش شمارش مجموع هاپ ها (بخشی از مسیر بین مبدا و مقصد) و همه پخشی ناخواسته در بین نودها در یک شبکه WNoC-DDs کمک می کند. نتایج تجربی نشان می دهد که معماری WNoC-DDs پیشنهادی سبب کاهش تاخیر ارتباط در مقایسه با معماری ها مش و WNoC-CD به ترتیب به میزان حداکثر 20.54 و 5.40 درصد می شود. به طور مشابه، معماری WNoC-DDs پیشنهادی سبب کاهش مصرف توان در مقایسه با معماری های مش و WNoC-CD به ترتیب به میزان حداکثر 73.56 و 19.97 درصد می شود.

1. مقدمه

فناوری های غالب همانند شبکه درون تراشه ای (Noc) مرسوم شده اند و می توانند محدودیت های عملکرد اتصالات متداول سیمی و سازنده را برای معماری های سیستم درون تراشه ای (SoC) حل کنند. مطالعات اخیر نشان می دهد محصولات زیادی همانند پردازنده ها، تلفن های سلولی، زیرسیستم های حفاظه و بسیاری دیگر از محصولات گنجانده شده بر روی یک تک تراشه ادغام می شوند و توسط شبکه درون تراشه ای به یکدیگر متصل می شوند [1-3]. طراحی سیستم های چند هسته ای سبب ساده شدن حل کارهای پیچیده با کار همزمان به صورت موازی همراه با بهبود سرعت اجرا و کاهش مصرف توان می شوند [4,5]. چند نخی (چند پردازشی) فرآیندی است که یک واحد پردازش مرکزی (CPU) می تواند تعداد متداولی از پردازش ها (نخ ها) را به طور همزمان اجرا کند. زمان بندی مبتنی بر حافظه متعادل شده یک روش زمان بندی پردازش است که سبب بهبود عملکرد از طریق ایجاد توازن در نیازمندی های دسترسی به حافظه می شود اما هزینه این کار عرض اتصالات داخلی و پهنای باند است [6].

6. نتیجه گیری ها

عملکرد معماری های پیشرفته شبکه درون تراشه (شبکه بر روی تراشه) به تاخیر ارتباط، تعداد هاپ ها و مصرف توان وابسته است. اگر مدت زمان راه اندازی ارتباط سریع باشد، انگاه عملکرد سیستم می تواند بهتر باشد. در این مقاله ما یک معماری WNoC همراه با دایرکتوری های توزیع شده (WNoC-DD) برای بهبود عملکرد به نسبت توان معرفی می کنیم. یک دایرکتوری به تسک ها اجازه می دهد تا با ارئه مسیر تطبیقی با حداقل مسیریابی برای دسترسی به نود مقصد عملکرد سریعی داشته باشند. ابزار VisualSim Architect برای مدل سازی و شبیه سازی معماری ها با استفاده از حجم کار تحلیلی مورد استفاده قرار می گیرد.

Abstract

Wireless Network-on-Chip (WNoC) architectures are introduced to improve performance by reducing the core-to-core communication latency. Conventional WNoCs broadcast messages that increase bandwidth-traffic, communication delay, and power consumption. Studies show that directory-based architectures have potential to address message broadcasting and improve performance. This work proposes a novel WNoC architecture with distributed directories (WNoC-DDs) that supports wireless communications to enhance faster execution by reducing latency. VisualSim software package is used to model and simulate the proposed WNoC-DDs, a WNoC with centralized directory (WNoC-CD), and a traditional 2D mesh by processing different communication scenarios. The proposed architecture helps reduce the total hop count and unwanted broadcasting among nodes in a WNoC-DDs. Experimental results show that the proposed WNoC-DDs reduces communication delay up to 20.54% and 5.40%, respectively, when compared to mesh and WNoC-CD. Similarly, the proposed WNoC-DDs reduces power consumption up to 73.56% and 19.97%, respectively, when compared to mesh and WNoC-CD.

1. Introduction

The dominant technology such as Network-on-Chip (NoC) is becoming trendy and can solve performance limitations of traditional wired interconnects and productive for System-on-Chip (SoC) architectures. Recent studies indicate that lot of products, such as, processors, cell phones, memory subsystems and many other embedded products are integrated on a single chip and interconnected by NoC [1–3]. The design of multicore systems makes easy to solve complex jobs by working concurrently in parallel with improved execution speed and reduced power consumption [4,5]. Multithreading is a process in which a central processing unit (CPU) can execute several number of threads simultaneously. Memory-balanced scheduling is a thread scheduling approach that improves the performance by balancing memory access requirements but at the cost of interconnects width and bandwidth [6].

6. Conclusions

Performance of modern Network-on-Chip architectures depends on communication latency, hop count, and power consumption. If the communication setup-time is quick, then the system performance should be better. In this work, we introduce a WNoC architecture with distributed directories (WNoC-DDs) to improve the performance to power ratio. A directory allows the tasks to execute faster by providing adaptive minimal routing path to reach the destination node. VisualSim Architect is used to model and simulate the architectures by using synthetic workload.

چکیده

1. مقدمه

2. مطالعه پیشینه

2-1 توپولوژی های محبوب شبکه

2-2 معماری WNoC

2-3 شبکه WNoC همراه با دایرکتوری متمرکز

3. دایرکتوری های توزیع شده پیشنهادی برای شبکه WNoC

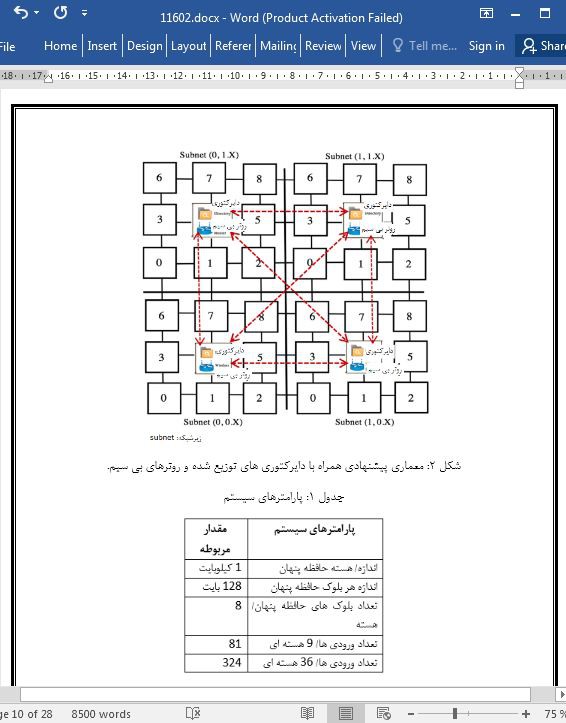

3-1 تفکیک هسته ها به درون زیرشبکه ها

3-2 طراحی دایرکتوری های توزیع شده

3-3 اصول کار دایرکتوری های توزیع شده

3-4 ارتباط درون و بیرون از زیرشبکه با استفاده از دایرکتوری های توزیع شده

4. جزئیات تجربی

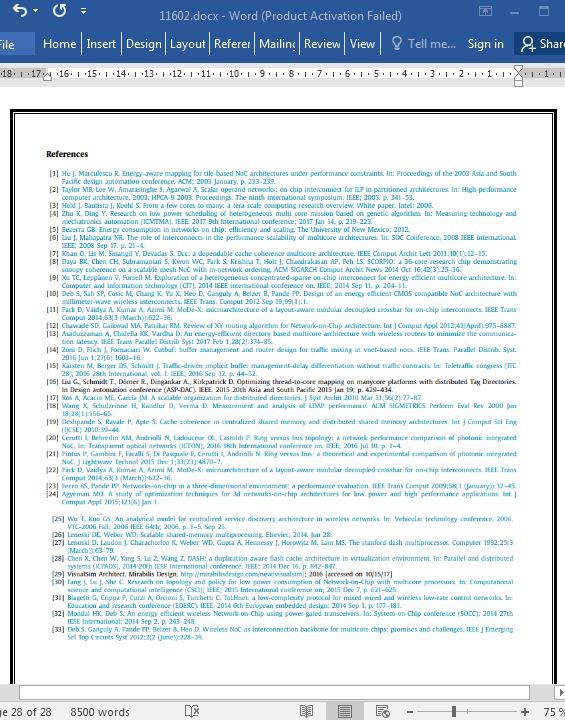

4-1 فرض ها

4-2 کارهای در دست اقدام

4-3 تعیین مسیر بین نودهای مبدا و مقصد

4-4 تعداد (شمارش) هاپ ها

4-5 مصرف توان

4-6 متوسط پارامترها برحسب درصد

5. نتایج و بحث

6. نتیجه گیری ها

منابع

Abstract

1. Introduction

2. Background study

2.1. Popular network topologies

2.2. WNoC architecture

2.3. WNoC with centralized directory

3. Proposed distributed directories for WNoC

3.1. Partitioning cores into subnets

3.2. Designing distributed directories

3.3. Working principle of distributed directories

3.4. In-Subnet and out-subnet communication using distributed directories

4. Experimental details

4.1. Assumptions

4.2. Tasks at hand

4.3. Determining route between source and destination nodes

4.4. Hop count

4.5. Power consumption

4.6. Average of parameters in percentage

5. Results and discussion

6. Conclusions

References

- اصل مقاله انگلیسی با فرمت ورد (word) با قابلیت ویرایش

- ترجمه فارسی مقاله با فرمت ورد (word) با قابلیت ویرایش، بدون آرم سایت ای ترجمه

- ترجمه فارسی مقاله با فرمت pdf، بدون آرم سایت ای ترجمه