پشتیبانی از دستیابی به حافظه همروند در معماری پردازشگرهای TCF

چکیده

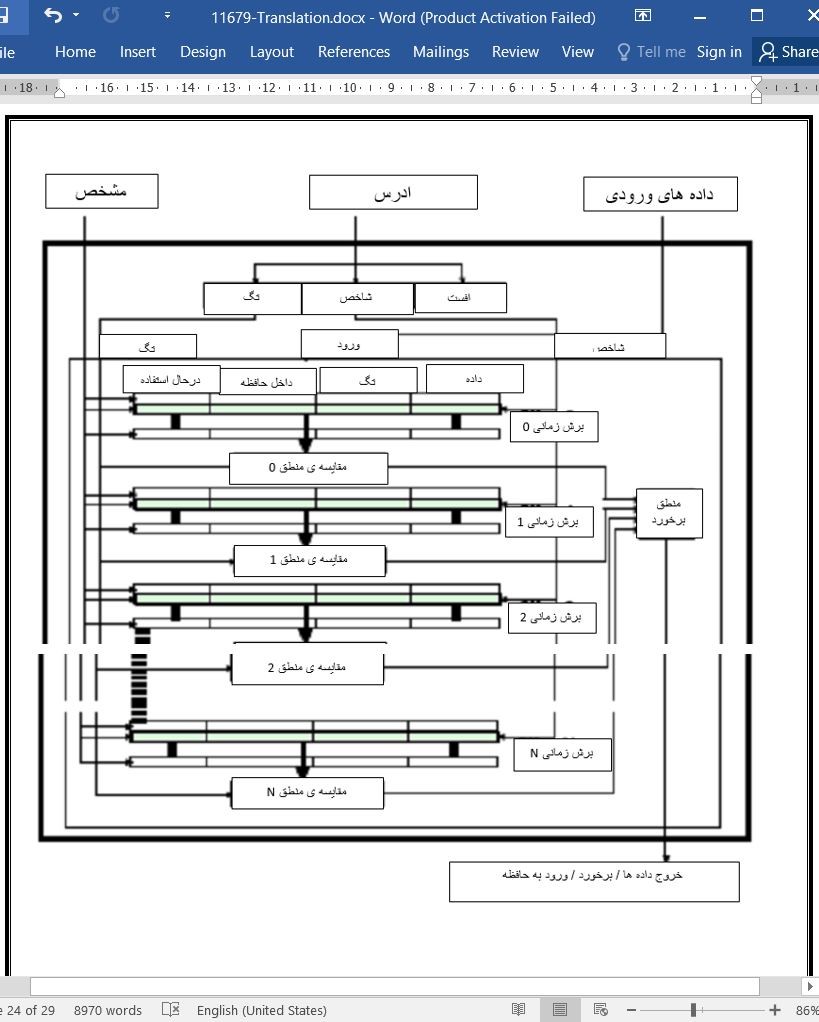

مدل روند کنترل ضخیم (TCF)، برنامه نویسی موازی را با دسته بندی محاسبات دارای روند یکسان در تک روندهایی که ضخامت گوناگونی دارند، اسان تر می سازد و پیش بینی می شود که بتواند کار مازاد بر احتیاج منابع نرم افزاری و سخت افزاری را کاهش دهد. در حالیکه معماری هایی که قادر به پشتیبانی از این مدل هستند، ارائه شده اند، پیشنهادهای کنونی نمی توانند از قابلیت دستیابی به حافظه ی همروند پشتیبانی کنند. این قابلیت می تواند هم برنامه نویسی را اسان سازد و هم سرعت بسیاری از الگوریتم های موازی را با عامل لگاریتمی افزایش دهد. در این مقاله، ما معماری های روند کنترل ضخیم (TCF) کنونی را توسعه می دهیم تا بتوانیم بطور موثر تری از دستیابی به خوانش همروند و حافظه ی نوشتاری پشتیبانی کنیم. راهکار پیش رو بر اساس حافظه ی پنهان محدود می باشد و از ساختار دو قسمتی، هیبریدی و فرانت اند – بک اند پردازشگرهای TCF کنونی استفاده می کند و در عین حال از ویژگی های تقارن مدل TCF نیز بهره می برد. بر اساس ارزیابی انجام گرفته بر اساس شبیه سازی، یک پردازشگر TCF با دستیابی به حافظه ی همروند با بک اند B می تواند الگوریتم هایی را با امکان دسترسی چند برابری به حافظه ی همروند نسبت به پردازشگر TCFی که از این قابلیت پشتیبانی نمی کند، اجرا نماید. سربار سخت افزاری در راهکار مورد نظر نسبتا کم براورد شده است. ما کد برنامه نویسی موازی را برای تشریح مزایای پشتیبانی از دستیابی به حافظه ی همروند در نظر قرار داده ایم.

1. مقدمه

مدل های برنامه نویسی استاندارد در پردازنده های چند هسته ای با حافظه ی اشتراکی، در معرض مجموعه ای از نخ های (ترد) رایانه ای قرار دارند که کدهای جداگانه را بصورت غیر همزمان به اجرا در می اروند (1، 2). در حالیکه این کار اجرای نخ های مستقل را اسان می سازد، وابستگی داده ها به یکدیگر در بین این نخ ها همزمان سازی صریح انها را بر اساس ساختارهایی مانند موانع، لاک ها و عملیات هسته ای ضروری می سازد تا این اطمینان حاصل شود که عملیات بحرانی در مسیر درست انجام شده است. از انجایی که هزینه ی اعمال این ساختارها با توجه به زمان اجرا و استفاده از منابع سخت افزاری در بسیاری از معماری های کنونی هسته های پردازشی و واحدهای پردازش گرافیکی بالا می باشد، وجود بسیاری از پارادایم های پیچیده و کارامد برای محاسبات موازی (3، 4، 5) غیر واقع بینانه به نظر می رسد. این پارادایم ها شامل: دستیابی به حافظه ی همروند که به پردازشگرها اجازه می دهد تا بطور همزمان یک مکان در حافظه را بخوانند و بنویسند و اجرای الگوریتم های ریز ساختار موازی می شوند.

5. نتیجه گیری

ما یک راهکار بر اساس معماری شبکه برای تحقق قابلیت دستیابی به حافظه ی همروند برای پردازشگرهای TCF ارائه نمودیم. این راهکار بر اساس کش های مرحله ای کراندار و یک ساختار دو قسمتی، هیبریدی، فرانت اند – بک اند در پردازشگرهای TCF می باشد. کش های مرحله ای، رفرنس های ایجاد شده را در حین اجرای مرحله ی بعدی ثبت می کنند. از انجایی که عملیات یک مرحله، بر اساس تعریف TCF مستقل است، هیچ گونه مشکلی در زمینه ی انسجام انها وجود ندارد. اگر یک عملیات همروند تک مکان در هر TCF وجود داشته باشد، واحد فرانت اند فعال می تواند دستیابی ها در سطح TCF را بطور اثر بخشی اجرا نماید. بر اساس ارزیابی های انجام شده، TPA واحد بک اند B که از دستیابی به حافظه ی همروند بهره می برد، می تواند الگوریتم های خاصی را تا B برابر سریعتر از TPA پایه اجرا کند. به کار گیری فرانت اند در زمینه ی دستیابی به حافظه ی همروند می تواند سرعت اجرا را افزایش دهد. هزینه ی تکنیک پیشنهادی در ناحیه ی سیلیکون و مصرف توان ان بسیار کم براورد شده است. مثال های برنامه نویسی ارائه شده نشان می دهند که دستیابی به حافظه ی همروند را می توان به عنوان یک الگوی دائمی در برنامه نویسی موازی در زبان های سطح بالا و اسمبلر به کار برد.

در اینده، هدف ما مطالعه ی بیشتر و توسعه ی سخت افزاری و علمی محاسبات بر مبنای TCF می باشد. این هدف با پیاده سازی مفهوم ثبات FPGA و مطالعه ی ان برای تحقق عملیات در زمینه ی پیشوندهای مختلف در معماری های TCF دنبال خواهد شد.

Abstract

The Thick Control Flow (TCF) model simplifies parallel programming by bundling computations with the same control flow into single flows of variable thickness, and has the prospect of alleviating redundant usage of software and hardware resources. While architectures that can support the TCF model have been proposed, current proposals cannot support concurrent memory accesses that can both simplify programming and speed up many parallel algorithms by a logarithmic factor. In this paper, we extend current TCF architectures to efficiently support concurrent read as well as write memory accesses. The solution is based on bounded size step-caches, and exploit the two-part, hybrid, frontend-backend structure of current TCF processors, and synchronization properties of the TCF model itself. According to our simulation-based evaluation, a concurrent memory access TCF processor with B backends can execute algorithms with substantial concurrent memory accesses up to B times faster than a baseline TCF processor not supporting concurrent memory access. The hardware overhead of the solution is estimated to be modest. We include parallel program code to illustrate the gains by supporting concurrent memory accesses.

1. Introduction

Standard programming models of current shared memory multicore processors expose sets of computational threads that execute individual code asynchronously [1, 2]. While this makes execution of independent threads straight-forward, data dependencies between threads make it necessary to explicitly synchronize them by constructs, like barriers, locks and atomic operations to guarantee that critical operations are carried out in the right order. Since the cost of applying these constructs in terms of execution time and usage of hardware resources is high in most current CPU and GPU architectures, many sophisticated and efficient paradigms for fine-grained parallel computing [3, 4, 5] are deemed impractical. These include concurrent memory access that lets a number of processors read and write a memory location concurrently, and execution of fine-grained parallel algorithms in general.

5. Conclusions

We have described an architectural solution to realize concurrent memory access for TCF processors. The solution is based on bounded size step caches and a two-part, hybrid, frontend-backend structure of current TCF processors. Step caches capture and hold the references made during the on-going step of an execution. Since operations within a step are independent by the definition of TCF execution, there are no coherence problems. If there is only a single-location concurrent operation per TCF, the active frontend unit can perform TCF-level accesses cost-efficiently. According to the evaluation, the concurrent memory access-aware B-backend unit TPA executes certain algorithms up to B times faster than the similarly configured baseline TPA. Employing the frontend in the case of single-location concurrent memory access can further speed up execution. The cost of the proposed technique in silicon area and power consumption is estimated to be very small. Our programming examples demonstrate that concurrent memory access can be integrated as a natural pattern of parallel programming in both high-level and assembler languages.

In the future we aim to further study and develop TCF-aware computing hardware and methodology. This includes an FPGA proof of concept implementation and studying the possibility to realize multiprefix operations on TCF architectures.

1. مقدمه

2. مدل TCF و معماری TPA

3. اجرای قابلیت دستیابی به حافظه ی همروند

3.1 ذخیره سازی مرحله ای

3.2 ساز و کارهای ارتباطی بک اند – فرانت اند

3.3 دسترسی همروند از طریق ذخیره سازی مرحله ای و انتشار/کاهش

4. ارزیابی

4.1 عملکرد

4.2 ملاحظات در اجرای تکنیک ها

4.3 مثال هایی از برنامه نویسی

5. نتیجه گیری

منابع

1. Introduction

2. TCF Model and TPA Architecture

3. Implementing Concurrent Memory Access

3.1. Step caching

3.2. Frontend backend communication mechanisms

3.3. Concurrent access via step caching and broadcasting/reduction

4. Evaluation

4.1. Performance

4.2. Implementation considerations

4.3. Programming examples

5. Conclusions

References

- اصل مقاله انگلیسی با فرمت ورد (word) با قابلیت ویرایش

- ترجمه فارسی مقاله با فرمت ورد (word) با قابلیت ویرایش، بدون آرم سایت ای ترجمه

- ترجمه فارسی مقاله با فرمت pdf، بدون آرم سایت ای ترجمه