دانلود رایگان مقاله مدارات مرجع برای LSI های CMOS نانووات

چکیده

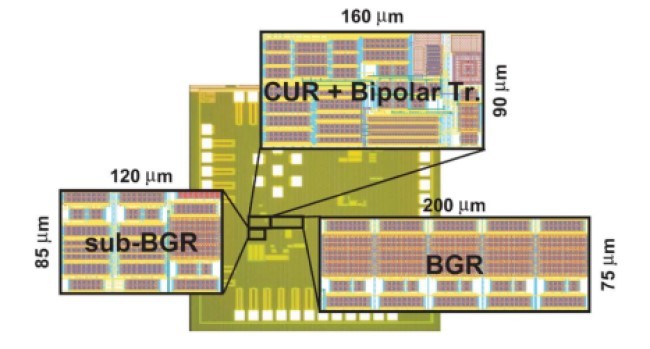

این مقاله منبع بندگپ و مدارات sub-BGR برای LSIهای نانووات را نشان میدهد. مدارات شامل یک مدار جریان مرجع نانوآمپری، یک ترانزیستور دوقطبی و ژنراتورهای ولتاژ متناسب با دمای خالص میباشند. مدارات پیشنهادی از استفاده از مقاومتها اجتناب کرده و شامل تنها MOSFET و یک ترانزیستور دوقطبی است. به دلیل اینکه مدار sub-BGR ولتاژ خروجی ترانزیستور دوقطبی را بدون استفاده از مقاومت تقسیم میکند، میتواند با منبع زیر 1ولت کار کند. نتایج تجربی به دست آمده در تکنولوژی CMOS 0.18 میکرومتر نشان میدهند که مدار BGRمیتواند ولتاژ مرجع 1.09ولت و مدار sub-BGR ولتاژ مرجع 0.548 را تولید کند. اتلاف توان مدارات BGR و sub-BGR به ترتیب 100 و 52.5 نانووات میباشد.

1. مقدمه

انتظار میرود که پیشرفت LSIهای نانووات منجر به گسترش نسل بعدی اپلیکیشنهایی با قابلیت نظارت توان، مثل وسیلههای پزشکی مرتبط با عمر و کمک کننده به زندگی، سنسورهای محیطی و شبکه سنسورهای بیسیم شود. ما نیاز داریم که LSIهایی طراحی کنیم که با اتلاف توان بسیار پایین کار کنند زیرا آنها باید برای مدت طولانی با منبع انرژی کمتر از حد ایدهآل که از میکروباتریها یا از انرژی طبیعی محیطی گرفته میشوند، عمل کنند. برای پیشرفت چنین LSIهایی، ما در ابتدا باید مدارات ولتاژ مرجع را توسعه دهیم زیرا از جمله مدارات سازنده آنالوگی پایهای هستند. در اینجا مدارت ولتاژ مرج مقاوم به تغییرات پروسه، ولتاژ و دما را که میتواند در دهها نانووات یا کمتر عمل کند، توصیف میکنیم.

مدارات BGR به طور گسترده در LSIهای مردن استفاده میشوند تا ولتاژ مرجع را درون چیپها تولید کنند. ولتاژ تولید شده برای پردازش سیگنال آنالوگ متنوعی استفاده میشود. با وجود اینکه BGRهای مختلفی توسعه داده شدهاند، اتلاف توان اکثر آنها از توان نانووات بشتر بوده و کاهش آن چشمگیر نبوده است. یکی از دلایل آن استفاده از مقاومتهاست. مقاومتها در اکثر مدارات مرجع برای تولید جریان و یا ولتاژ برای کنترل ویژگیهای دمایی ولتاژ مرجع خروجی استفاده میشود. وقتی از یک مقدار میانه برای مقاومت استفاده میشود جریان کافی برای مقاومتها نیاز بوده و لذا اتلاف توان نمیتواند کاهش یابد. در صورتی که برای کاهش جریان مقاومت بزرگتر در نظر گرفته شود مساحت سطح سیلیکون افزایش مییابد.

مدارات مرجع بدون مقاومتی که در توان نانوواتی کار میکنند گزارش شدهاند. اگرچه، خروجی ولتاژ مرجع این مدارات با تغییرات پروسه تغییر میکند، زیرا به ولتاژ آستانه ماسفتها بستگی دارند. لذا برای استفاده به عنوان مدار ولتاژ مرجع مناسب نیستند.

در این مقاله یک مدار BGR نانوواتی که از مقاومت استفاده نمیکند ارائه میشود. در تضاد با Hirose et al از یک تکنولوژی CMOS 0.18 میکرومتر متفاوتی استفاده کرده تا استحکام معماری مدار BGR خود را نشان دهیم. BGR پیشنهادی شامل یک مدار جریان مرجع نانوآمپری، یک ترانزیستور دوقطبی و یک ژنراتور ولتاژ PTAT میباشد. چون این مدار فقط شامل ماسفتها و یک ترانزیستور دوقطبی است، میتواند یک ولتاژ بندگپ بدون مقاومت را تولید کند. علاوه بر آن یک مدار sub-BGR که ولتاژ کمتر از 1.2ولت را تولید میکند نیز ارائه میشود. Sub-BGR پیشنهادی از یک مقسم ولتاژ استفاده میکند. مقسم ولتاژ، ولتاژ بیس-امیتر دوقطبی را در ورودی گرفته و در ترکیبی از ژنراتورهای ولتاژ PTAT، یک ولتاژ مرجع کمتر از 1ولت را تولید میکند لذا sub-BGR پیشنهادی به عنوان یک مدار مرجع در LSIهای کمتر از 1ولت مفید است.

این مقاله به این ترتیب سازماندهی شده است که بخش II اصول عملکرد نهفته در مدارات پیشنهادی را ارائه میکند. بخش III پیادهسازی مدارات با استفاده از تکنولوژی 0.18 میکرومتر و N-well عمیق را توصیف کرده و نتایج تجربی با چیپ ساخته شده ارائه میشود. اتلاف توان بسیار کم 100 و 52.5 نانووات برای مدارات BGR و sub-BGR حاصل شدند. بخش IV نتیجه مقاله میباشد.

2. معماری

A. ویژگیهای جریان subthreshold

عملکرد در subthreshold به توان بسیار پایین منجر میشود زیرا جریان در ان در حد نانوآمپر است.

BGR .B

شکل 1 معماری مدار BGR پیشنهادی را نشان می دهد. از یک مدار مرجع جریان نانو آمپر، یک ترانزیستور دوقطبی و یک ژنراتور ولتاژ PTAT تشکیل شده است.

Abstract

This paper presents bandgap reference (BGR) and sub-BGR circuits for nanowatt LSIs. The circuits consist of a nano-ampere current reference circuit, a bipolar transistor, and proportional-to-absolute-temperature (PTAT) voltage generators. The proposed circuits avoid the use of resistors and contain only MOSFETs and one bipolar transistor. Because the sub-BGR circuit divides the output voltage of the bipolar transistor without resistors, it can operate at a sub-1-V supply. The experimental results obtained in the 0.18- m CMOS process demonstrated that the BGR circuit could generate a reference voltage of 1.09 V and the sub-BGR circuit could generate one of 0.548 V. The power dissipations of the BGR and sub-BGR circuits corresponded to 100 and 52.5 nW.

I. INTRODUCTION

THE development of nanowatt LSIs is expected to lead to the expansion of next-generation power-aware applications such as life-log and life-assist medical devices, environmental sensors, and wireless sensor networks [1], [2]. Because they must operate for a long time with less-than-ideal energy supply from microbatteries or from surrounding natural energy, we need to design LSIs that operate with extremely low power dissipation. To develop such LSIs, we must first develop voltage reference circuits because they are one of the most fundamental analog building circuits. Here, we describe process, voltage, and temperature (PVT) variation-tolerant voltage reference circuits that can operate at several tens of nanowatts or less.

Bandgap reference (BGR) circuits are widely used in modern LSIs to generate a reference voltage on chips. The generated voltage is used for various analog signal processes. Although several BGRs have been developed, the power dissipations of most of them exceed nanowatt power [3]–[7] and have not been significantly reduced. One reason for this is the use of resistors. The resistors in most reference circuits are used to generate current or voltage to control the temperature characteristics of the output reference voltage [3]–[9]. When we use a moderate value for resistance, sufficient current for the resistors is required and power dissipation therefore cannot be reduced. Although it can be reduced if we accept using a large value for resistance, the resistors will occupy a large area of the silicon.

Resistor-less voltage reference circuits that operate at nanowatt power have been reported [10]–[12]. However, because the output reference voltages of these circuits are based on the threshold voltage of MOSFETs, the voltages will change with process variations [10]–[12]. Therefore, they are not suitable for use as voltage reference circuits.

This paper presents a nanowatt BGR circuit that does not use resistors [13]. In contrast to Hirose et al. [13], we use a different 0.18- m CMOS process to demonstrate the robustness of our BGR circuit architecture. The proposed BGR consists of a nano-ampere current reference circuit, a bipolar transistor, and proportional-to-absolute-temperature (PTAT) voltage generators. Because the circuit only consists of MOSFETs except for the bipolar transistor, it can generate a bandgap voltage without resistors. In addition, a sub-BGR circuit that generates voltage lower than 1.2 V is also presented. The proposed sub-BGR uses a voltage divider. The voltage divider accepts the base-emitter voltage of the bipolar transistor and generates a sub-1-V reference voltage in combination with the PTAT voltage generators. Therefore, the proposed sub-BGR is useful as a reference circuit in sub-1-V LSIs.

This paper is organized as follows. Section II presents the operating principles behind our proposed circuits. Section III describes the implementation of the circuits using 0.18- m CMOS process technology with deep N-well option and presents the experimental results with a fabricated proof-of-concept chip. Extremely low power dissipation of 100 nW for the BGR and 52.5 nW for the sub-BGR were achieved. Section IV concludes the paper.

II. ARCHITECTURE

A. Characteristics of Subthreshold Current

Subthreshold operation achieves ultralow-power operation because the subthreshold current is of the order of nano-amperes.

B. BGR

Fig. 1 shows the architecture of the proposed BGR circuit. It consists of a nano-ampere current reference circuit, a bipolar transistor, and a PTAT voltage generator.

چکیده

1. مقدمه

2. معماری

A. ویژگیهای جریان subthreshold

BGR .B

3. نتایج تجربی

A. پیادهسازی مدار

B. نتایج

C. مباحثه

4. نتیجهگیری

منابع

Abstract

1. INTRODUCTION

2. ARCHITECTURE

A. Characteristics of Subthreshold Current

B. BGR

3. EXPERIMENTAL RESULTS

A. Circuit Implementation

B. Results

C. Discussion

4. CONCLUSION

REFERENCES