دانلود رایگان مقاله یک SAR ADC خط لوله ای تک تقویت کننده عملیاتی ۴ مرحله ای

چکیده

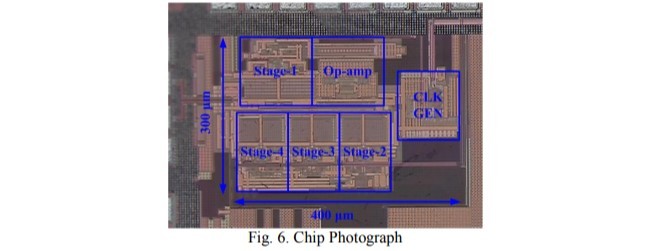

این مقاله یک راهاندازی خط لولهای ۴ مرحلهای ۱۲ بیت 110 MS/s یکپارچه SAR ADC را از طریق یک تک تقویتکننده عملیاتی با بهره پایین ارائه میدهد. یک تکنیک مبتنی بر نسبت کالیبراسیون خطای بهره بر اساس به اشتراکگذاری تک تقویتکننده عملیاتی بهمنظور کاهش پیچیدگی مدار دیجیتالی کالیبراسیون پیشنهادشده است. تنها یک سیگنال عدد شبه تصادفی برای انجام تزریق لرزش به کار گرفتهشده است، اما خطاهای متعدد بهره را کالیبره میکند، و درنتیجه تسریع سرعت همگرایی، رهایی از کاهش سیگنال ورودی و به حداقل رساندن اصلاح آنالوگ با توجه به کالیبراسیون پسزمینهای را انجام میدهد. اثربخشی معماری در تراشههای ۶۵ نانومتری CMOS که مساحت هسته آنالوگ آنها تنها mm20.12 است، تأیید شده است. ADC بهطور متوسط ۶۳ دسیبل SNDR و ۷۵٫۲ دسیبل SFDR را در 110 MS/s با مصرف توان آنالوگ ۱۱٫۵ میلی وات از یک منبع ۱٫۲ ولت به دست میآورد. تنها ۴۰ هزار نقطه برای رسیدن به SNDR مطلوب با روش کالیبراسیون ارائهشده موردنیاز است.

1. مقدمه

در حال حاضر با مصرف توان کمتر بهصورت ذاتی، SAR ADC خط لولهای [۱] [۲] به یک توپولوژی جایگزین محبوب برای خط لوله مرسوم ADC تبدیل شده است. اتلاف توان کمتر، از MDAC سادهشده به دست میآید و تعداد مقایسهگرها را به دلیل جایگزینی فلاش با SAR در هر یک از زیر مرحلههای ADC به حداقل رسانده است. یک تک تقویتکننده عملیاتی با دو گام خط لولهای غالباً در طرحهای قبلی [۱] [۲] برای خط لوله SAR ADC به کار گرفتهشده است، اما برای رسیدن به سرعت بالا و وضوح بالا (> ۱۰ بیت) با توجه به نوسان کوچک سیگنال باقیماندهاش بیشازحد مرزی است. از سوی دیگر، خط لوله چندمرحلهای، دارای مزایای به دست آوردن فضای بیشتر از طریق معاوضه بهتر در تخصیص وضوح هر یک از زیر مراحل که برای وضوح بالاتر بسیار مهم است، چندین تقویتکننده عملیاتی برای MDAC و مقدار نوسان باقیمانده است. بااینوجود، چندین تقویتکننده عملیاتی در ساختار خط لوله چندمرحلهای مرسوم اجتنابناپذیر است، مگر اینکه روش به اشتراکگذاری زمان [۳] استفاده شود، که قابلاستفاده برای خط لوله SAR ADC است.

همانطور که تکنولوژی سیلیکون به سمت مقیاس عمیقتر از زیر میکرون در حال حرکت است، طراحی تقویتکننده عملیاتی برای رسیدن به بهره بالای حلقه باز توسط بهره پایین ذاتی ترانزیستور و منبع ولتاژ سختتر میشود. بنابراین، استفاده از یک تقویتکننده عملیاتی بهره کم با کالیبراسیون دیجیتال میتواند مزایا را از روند ریزمقیاس نمایی حفظ کند. چند تکنیک کالیبراسیون پسزمینهای [۴] [۵] برای ADC خط لولهای چندمرحلهای برای جبران بهره پایین تقویتکننده عملیاتی در حوزه دیجیتال ارائهشده است.

روش مبتنی بر برابرسازی [۴] یک ماکت مجازی ADC را در حوزه دیجیتال با استفاده از درونیابی غیرخطی برای کالیبره کردن ADC واقعی به کار میگیرد، اما آن در باند سیگنال ورودی محدود و سختافزار بزرگ برای ماکت ADC نتیجه میشود. روش مبتنی بر لرزش [۵]، یک دنباله پالس عدد شبه تصادفی را برای استخراج خطاها از MDAC بدون محدودیت پهنای باند سیگنال ورودی تزریق میکند. بااینحال، این روش از کاهش دامنه سیگنال و زمان طولانی همگرایی رنج میبرد.

این مقاله یک SAR ADC خط لولهای ۴ مرحلهای ۱۲ بیت 110 MS/s را در فرآیند ۱۲ نانومتری CMOS ارائه میدهد. روش مبتنی بر زمانبندی برای به اشتراک گذاشتن یک تک تقویتکننده عملیاتی برای باقیمانده تقویت بین مراحل خط لوله SAR ارائهشده است، که در آن سه مرحله غیر همپوشان برای به حداکثر رساندن افزایش زمان تقویتکننده عملیاتی و بیتهای قابلاستفاده در هر دوره از نمونهبرداری اختصاص دادهشده است. علاوه بر این، تکنیک مبتنی بر نسبت کالیبراسیون خطای بهره بر اساس به اشتراکگذاری تقویتکننده عملیاتی برای بهکارگیری تنها یک سیگنال عدد شبه تصادفی برای برآورد خطاهای متعدد بهره توسط یک خطای مطلق بهره MDAC ثانویه و نسبت مقایسهای بین دیگر MDACها ارائهشده است، که سرعت همگرایی را تسریع میکند، اصلاح آنالوگ و سربار دیجیتال را به حداقل میرساند، و از کاهش سیگنال ورودی با توجه به کالیبراسیون پسزمینهای خلاص میشود.

2. روشها و معماری پیشنهادی ADC

بلوک دیاگرام SAR ADC خط لولهای پیشنهادی با کالیبراسیون پسزمینهای دیجیتال در شکل ۱ نشان دادهشده است. این بلوک دیاگرام از سه مرحله SAR خط لولهای ۴ بیتی و یک مرحله SAR پایانی ۵ بیتی تشکیلشده است. علاوه بر این، با هدف مصرف توان کمتر، هر زیر مرحله SAR از روش سوئیچینگ VCM و روش عاری از میانیگر مرجع برای حذف نردبان مرجع از تمام مراحل [۲] استفاده میکند. بهرههای حلقه بسته از سه MDAC اول عیناً بهعنوان ۴ برای یک معاوضه بهتر بین سرعت تقویتکننده عملیاتی و DNL توسط تخریب واحد کوچکتر خازن در MDAC اختصاص دادهشدهاند.

فقط یک تقویتکننده عملیاتی توسط همه ۴ مرحله از طریق روش مبتنی بر زمانبندی برای تقویت در شکل ۲ ارائهشده است. همانطور که در شکل ۲ نشان دادهشده است، با توجه به غیر همپوشانی بودن مرحله تقویت بین هر مرحله و مرحله عدم تقویت برای آخرین مرحله، یک تک تقویتکننده عملیاتی دائماً از طریق ۴ مرحله به اشتراک گذاشتهشده است و آخرین مرحله، زمان تبدیل SAR طولانیتری را نشان میدهد. علاوه بر این، سه قسمت از سه مرحله اول، همان مقدار از زمان را برای معاوضه بهتر بین سرعت سیستم و خطی سازی تقویتکننده عملیاتی موردنیاز اشغال میکنند. بنابراین، الگوی توزیع بیت از نمودار زمانبندی تعیین میشود، که تعداد مشابه بیتها در سه مرحله اول و بیتهای بیشتر در آخرین مرحله وجود دارد.

بهمنظور کاهش نیاز بهره از تک تقویتکننده عملیاتی و افزایش سرعت سیستم، تقویتکننده عملیاتی با بهره کم استفادهشده است و روش مبتنی بر نسبت کالیبراسیون خطای بهره بر اساس به اشتراکگذاری تقویتکننده عملیاتی برای کالیبره کردن سریع خطاهای بهره در هر مرحله تقویت ارائهشده است، که بهعنوان معادلات زیر نشان دادهشده است.

Abstract

This paper presents a 12-bit 110MS/s 4-stage pipelined SAR ADC integrated through a single low-gain op-amp. A ratiobased GEC (Gain Error Calibration) technique based on op-amp sharing is proposed to reduce the complexity of digital calibration circuit. Only one PN (Pseudo-random Number) signal is employed to perform the dither injection but calibrate multiple gain errors, and thus accelerates the convergence speed, gets rid of input signal reduction and minimizes the analog modification due to the background calibration. The effectiveness of the architecture is verified in 65-nm CMOS chips whose analog core area is 0.12 mm2 only. The ADC obtains an average SNDR of 63 dB and SFDR of 75.2 dB at 110MS/s consuming analog power of 11.5mW from a 1.2-V supply. Only 40 thousand points are needed to achieve desirable SNDR with the proposed calibration technique.

I. INTRODUCTION

With its intrinsic lower power consumption, pipelined SAR ADC [1] [2] has already become a popular alternative topology for traditional pipeline ADC. The less power dissipation is derived from its simplified MDAC and minimized number of comparators due to the replacement of the flash with SAR in each sub-stage ADC. A single op-amp with two-step pipelined stages is frequently employed in the previous designs [1][2] for pipeline SAR ADC, but is too potentially marginal to achieve both high speed and high resolution (>10-bit) due to small swing of its residue signal. Multi-stage pipeline, on the other hand, has the benefit of gaining more headroom, which is crucial for higher resolution, through the better tradeoff among resolution allocation of each sub-stage, amplification factor for MDAC and magnitude of residue swing. Nevertheless, multiple op-amps are inevitable in the traditional multi-stage pipeline structure, unless time-sharing technique [3] is utilized, which is not applicable for pipeline SAR ADC.

As the silicon technology is keeping on moving towards deeper sub-micron scale, the design of op-amp becomes harder to achieve high open-loop gain by the lower intrinsic gain of transistor and voltage supply. Therefore, using a low-gain opamp with the digital calibration can keep benefiting from the process downscaling. Several background calibration techniques [4][5] have been proposed for multi-stage pipelined ADCs to compensate low gain of op-amps in digital domain.

The equalization-based technique [4] employs a virtual replica ADC in the digital domain using nonlinear interpolation to calibrate the real ADC, but it results in band limited input signal and large hardware for the replica ADC. The ditheringbased technique [5] injects a PN pulse sequence to extract errors from MDAC without the input-signal bandwidth limitation. However, it suffers from signal range reduction and long convergence time.

This paper presents a 12-bit, 110MS/s 4-stage pipelined SAR ADC in 65nm CMOS process. A timing-derived technique is proposed to share a single op-amp for residue amplification between pipelined SAR stages, where three nonoverlap phases are allocated to maximize both usable bits and op-amp amplification time in each sampling period. Besides, a ratio-based GEC technique based on op-amp sharing is proposed to employ only one PN signal to estimate multiple gain errors by one absolute gain error of the second MDAC and comparative ratios between other MDACs, which accelerates the convergence speed, minimizes the analog modification and digital overhead, and gets rid of input signal reduction due to the background calibration.

II. PROPOSED ADC ARCHITECTURE AND TECHNIQUES

The block diagram of the proposed pipelined SAR ADC with background digital calibration is shown in Fig. 1. It consists of three 4-bit pipelined SAR stages and one 5-bit backend SAR stage. Besides, with the purpose of lower power consumption, each SAR sub-stage makes use of Vcmswitching technique, and reference buffer free technique to remove reference ladders of all stages [2]. Close-loop gains of the first three MDACs are assigned identically as 4 for a better tradeoff between speed of op-amp and DNL degraded by smaller unit capacitor in MDAC.

Only one op-amp is utilized for amplifications by all four stages through the proposed timing-derived technique in Fig. 2. Due to both of the non-overlapping of amplification phase between each stage and no amplification phase for the last stage as shown in Fig. 2, a single op-amp is shared through four stages incessantly and the last stage exhibits longer SAR conversion time. Besides, three phases of the first three stages occupy the same amount of time for a better tradeoff between the system speed and op-amp linearity requirement. Therefore, the bit distribution pattern that there is the same number of bits in the first three stages and more bits in the last stage is decided from the timing diagram.

In order to alleviate the gain requirement of the single opamp and boost the system speed, low gain op-amp is used and a ratio-based GEC technique based on op-amp sharing is proposed to calibrate its gain errors rapidly in each amplification phase, which is manifested as the following equations.

چکیده

1. مقدمه

2. روشها و معماری پیشنهادی ADC

3. پیادهسازی مدارها

.A آرایههای MDAC

.B تقویتکننده عملیاتی با بهره کم آیینه جریان سرعت بالا

.C تخمین نسبت بهره

4. نتایج اندازهگیری

5. نتیجه گیری

منابع

Abstract

1. INTRODUCTION

2. PROPOSED ADC ARCHITECTURE AND TECHNIQUES

3. CIRCUITS IMPLEMENATION

A. MDAC Arrays

B. High Speed Current-mirror Low-Gain Op-Amp

C. Gain Ratio Estimation

4. MEASUREMENT RESULTS

5. CONCLUSION

REFERENCES