دانلود رایگان مقاله یک ADC خط لوله 12 بیتی با استفاده از یک جلودار تیپ دلو پالسی

چکیده

یک ADC خط لوله کم توان، پر سرعت، توسط جایگزینی آمپلی فایرهای باقیمانده جلو دار با مدار بندی تیپ دلو پالسی و توسط جبران کردن خطاهای ورودی با استفاده از خطی سازی دیجیتال، پیاده می شود. ADC در CMOS 65 نانومتری پیاده سازی شده و 0.26 میلی متر مربع جا اشغال می کند. این در 200MS/s کار می کند، 11.5 Mw از یک منبع 1 ولتی مصرف کرده و به SNDR معادل 65 دسی بل در فرکانس های ورودی پایین و 57.6 دسی بل نزدیک نایکوئیست دست می یابد. Schreier FOM مبتنی بر SNDR متناظر به ترتیب 164.5 و 157 دسی بل است.

مقدمه

بیشتر توان در مراحل ADC خط لوله معمول توسط آمپلی فایرهای عملیاتی مصرف می شود که باقیمانده مرحله را تولید می کند. برای کاهش توان کل ADC، متدهای تقویت جدید کشف می شوند. در [1] یک مدار تیپ دلو برای فعال کردن تولید باقیمانده موثر استفاده می شود. اما، این طرح هنور به OpAmps کمکی برای ته نشانی دقیق و کامل متکی می باشد، این صرفه جویی های قابل دست یافت را محدود می کند. این کار بر مبنای [1]، توسط حذف OpAmps کمکی و به کار انداختن مدار در ولتاژ منبع پایین در یک فرایند خط-پالایش ، بهبود انجام می دهد. خطاهای باقیمانده نتیجه شده از حذف OpAmps از طریق خطی سازی دیجیتال نشانی دهی می شوند.

اصل اساسی مورد استفاده در مراحل خط لوله تیپ دلو، تقویت انتقال شارژ (بار) است، که این بار از یک خازن بزرگ به یک خازن کوچک منتقل می شود تا بهره ولتاژ به دست آید. عمل یک مدار تیپ دلو تقویت شده با OpAmp معمولی در شکل 1 الف دیده می شود. در حین ، ورودی روی نمونه برداری می شود، و در حین بار توسط اعمال کردن یک زمین مجازی در نود درون مجددا توزیع می شود. با بهره OpAmp بزرگ ، بهره ولتاژ نتیجه دقیقاً به نسبت تنظیم می شود. الزامی ترین جنبه این مدار این است که بار ورودی نمونه گیری شده، برای شارژ کردن خروجی دوباره استفاده می شود. این متفاوت از یک خط لوله خازن سوئیچ شده ی سنتی است، که هر مرحله یک بسته بار جدید از منبع گرفته و بار ورودی اش اساساً تلف می شود.

شکل 1 ب ، پیاده سازی کم- OpAmp پیشنهادی را نشان می دهد. گیت ترانزیستور گذر توسط یک پالس ولتاژ هدایت می شود که از رفتار خروجی OpAmp در حین گذار اولیه تقلید می کند. مخصوصا، توجه کنید که OpAmp در شکل 1 الف بدواً با یک پالس زمان خیزش محدود پاسخ می دهد تا انتقال بار را تسریع نماید (خط پر رنگ برچسب خورده با ). یک افزایش سرعت مشابه در پیاده سازی ما توسط گیت بندی ترانزیستور با یک پالس تولید شده توسط یک مدار RC به دست می آید. تفاوت اصلی بین دو مدار این است که پیاده سازی کم-OpAmp دقیقا ته نشانی نمی کند. در پایان ، نود حاوی خطاهای خطی و غیر خطی وابسته به سیگنال است که می تواند با دما تغییر کند (مثلا به دلیل شیفت های Vt). در ADC پیشنهادی، این مساله توسط خطی سازی دیجیتال و کالیبراسیون پس زمینه پیوسته کاهش می یابد.

معماری ADC و طراحی مدار

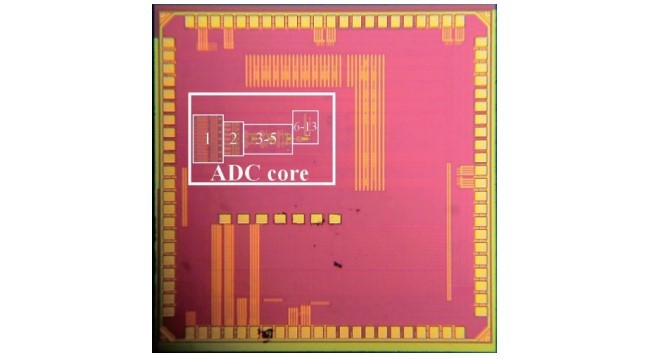

شکل 2 بلوک دیاگرام طرح اثبات مفهوم 13 مرحله ای ما را نشان می دهد. دو تای اول و بحرانی ترین مرحله از مدار شکل ب استفاده می کند و برای بهره ولتاژ 3.1 طراحی شده است. برای کاهش سربار کالیبراسیون، سه مرحله بعدی با استفاده از توپولوژی مبتنی بر OpAmp شکل 1 الف با بهره 2 پیاده سازی می شوند. عقبه 8 مرحله ای با استفاده از مراحل خازن سوئیچ شده مبتنی بر OpAmp 1.5 بیتی سنتی پیاده سازی می شود.

شکل 3 شمای مدار نصفه مرحله 1 را نشان می دهد. پیاده سازی واقعی شبه تفتضلی است و از دو کپی این مدار استفاده می کند. مرحله در چهار فاز زمان بندی می شود : قبل از شارژ (فاز کوتاه)، نمونه، مقایسه (فاز کوتاه) و توزیع دوباره شارژ.

در فاز نمونه، ورودی بصورت موازی روی دو خازن با اندازه برابر نمونه گیری می شود. در حین فاز مقایسه، صفحات بالایی این خازن ها به ک ولتاژ مد مشترک متصل می شوند و مقایسه گر ها برای کمی کردن درشت (تقریبی) ورودی فعال سازی می شوند. در فاز توزیع دوباره بعدی، صفحه بالایی یکی از خازن های نمونه برداری کننده به ولتاژ مرجع متصل شده و دیگری به همتای آن در مدار نیمه بعدی متصل می شود. این بهره مد مشترک را به اندازه واحد کاهش داده و بنابراین به ما اجازه می دهد تا مراحل شبه تفاضلی را بدون تنزل مد مشترک قابل توجه از مرحله ای به مرحله دیگر اتصال متوالی کنیم.

برق پذیری های DAC در حین فاز نمونه به ولتاژ مرجع شارژ می شوند. در حین توزیع مجدد، سوئیچ های DAC مطابق با تصمیم های مقایسه گر تنظیم شده و برای انتقال بار سریع به مرحله بعدی باردار می شود، طبق توضیح بالا. چون ورودی مرحله 1 یک ولتاژ است، فاز پیش از باردار شدن استفاده نمی شود. در مراحل 2-5، که روی بار ورودی عمل می کند، فاز پیش-شارژ برای مقدار دهی اولیه ولتاژ نود ورودی پیش از دریافت بار از مرحله راندن آن خدمت می کند.

Abstract

A high-speed, low-power pipeline ADC is realized by replacing the front-end residue amplifiers with pulsed bucket brigade circuitry and compensating for the introduced errors using digital linearization. The ADC is implemented in 65- nm CMOS and occupies 0.26 mm2 . It operates at 200 MS/s, consumes 11.5 mW from a 1-V supply and achieves an SNDR of 65 dB at low input frequencies and 57.6 dB near Nyquist. The corresponding SNDR-based Schreier FOM is 164.5 dB and 157 dB, respectively.

Introduction

Most of the power in conventional pipeline ADC stages is consumed by the operational amplifiers that generate the stage residue. In order to reduce the total power of the ADC, new amplification methods are being explored. In [1] a bucket brigade circuit is used to enable efficient residue generation. However, this scheme still relies on auxiliary OpAmps to achieve complete and precise settling, which limits the achievable savings. This work improves upon [1] by eliminating the auxiliary OpAmps and operating the circuit at a low supply voltage in a fine-line process. The residue errors resulting from the removal of the OpAmp are addressed through digital linearization [2].

The core principle used in bucket brigade pipeline stages is charge transfer amplification [3], where charge is moved from a large capacitor to a small capacitor to realize voltage gain. The operation of a conventional OpAmp-boosted bucket brigade circuit [4] is illustrated in Fig. 1(a). During φ1, the input is sampled on Cin, and during φ2 the charge is redistributed onto CL by forcing a virtual ground at node VS. With large OpAmp gain, the resulting voltage gain is precisely set to the ratio Cin/CL. The most compelling aspect of this circuit is that the sampled input charge is re-used to charge the output. This is very different from a traditional switched capacitor pipeline, where each stage draws a new charge packet from the supply and its input charge is essentially wasted.

Fig. 1(b) shows the proposed OpAmp-less realization. The gate of the pass transistor is driven by a voltage pulse that mimics the behavior of the OpAmp output during the initial transient. Specifically, note that the OpAmp in Fig. 1(a) initially responds with a finite rise time pulse to speed up the charge transfer (bold line labeled VG). A similar speed-up is achieved in our realization by gating the transistor with a pulse generated by an RC circuit. The main difference between the two circuits is that the OpAmp-less realization does not settle precisely. At the end of φ2, node VS contains signal dependent linear and nonlinear errors that can drift with temperature (e.g., due to Vt shifts). In the proposed ADC, this issue is mitigated though digital linearization and continuous background calibration.

ADC Architecture and Circuit Design

Fig. 2 shows the block diagram of our 13-stage proof-ofconcept design. The first two and most critical stages use the circuit of Fig. 1(b) and are designed for a voltage gain of 3.1. To reduce the calibration overhead, the next three stages are implemented using the OpAmp based topology of Fig. 1(a) with a gain of 2. The 8-stage backend is implemented using traditional 1.5-bit OpAmp-based switched capacitor stages.

Fig. 3 shows the half circuit schematic of stage 1. The actual implementation is pseudo-differential and uses two copies of this circuit. The stage is timed in four phases: precharge (short phase), sample, compare (short phase) and charge re-distribution.

In the sample phase, the input is sampled in parallel on two equally sized capacitors (Cin/2). During the compare phase, the top plates of these capacitors are connected to a common mode voltage and the comparators are activated to coarsely quantize the input. In the following redistribution phase, the top plate of one of the sampling capacitors is connected to the reference voltage VL and the other is connected to its counterpart in the other half circuit. This reduces the common mode gain to unity and thus allows us to cascade pseudo-differential stages without significant common-mode deterioration from stage to stage.

The DAC capacitances are charged to the reference voltages during the sample phase. During redistribution, the DAC switches are set according to the comparator decisions and VG is pulsed for fast charge transfer to the next stage, as explained above. Since the input of stage 1 is a voltage, the pre-charge phase is not used. In stages 2-5, which operate on input charge, the pre-charge phase serves to initialize the input node voltage prior to receiving charge from its driving stage.

چکیده

مقدمه

معماری ADC و طراحی مدار

نتایج سنجش

منابع

Abstract

Introduction

ADC Architecture and Circuit Design

Measurement Results

References