دانلود رایگان مقاله محدودکننده گذرای حالت-جامد برای حالات گذار سوییچینگ بانک خازنی

چکیده

اضافه ولتاژ گذرا و جریان هجومی, دو پدیده عمده گذرا هستند که به خاطر سوییچینگ خازن رخ می دهند. علاوه بر تنزل کیفیت توان، این موارد گذرا منجر به کوتاه شدن طول عمر خازن و دستگاه سوییچینگ می شوند. به منظور کاهش این حالات گذرا، یک محدودکننده گذرای سوییچینگ خازن حالت جامد(SSCSTL) در این مطالعه پیشنهاد شده است.SSCSTL پیشنهادی دارای دو حالت عملیات است: حالت محدودکننده و حالت کنارگذر. در طول انرژی زایی خازن، یک راکتور DC و یک وریستور, جریان هجومی و اضافه ولتاژ گذرا را حذف می کند. در حالت پایدار، راکتور DC توسط یک تریستور کنارگذر می شود، به طوری که SSCSTL به صورت اتصال کوتاه عمل می کند و هیچ اثر قابل توجهی بر روی مدار ندارد. تریستور با استفاده از یک تکنیک جدید خودکار راه اندازی ساختار ساده در شرایط عادی تحریک می شود. SSCSTL پیشنهادی با یک ساختار بسیار ساده و همچنین عملکرد سریع و قابل اعتماد, یک راه حل کارآمد برای اطمینان از سوییچینگ خازن بدون هیچ اضافه ولتاژ و گذرا و جریان هجومی است. یک SSCSTL نمونه اولیه تک فاز توسط برنامه گذرای الکترومغناطیسی شبیه سازی شده و تست شده است. نتایج شبیه سازی و آزمایش نشان می دهد که SSCSTL پیشنهادی موجب کاهش قابل ملاحظه جریان هجومی و اضافه ولتاژ گذرا در طول سوییچینگ خازن می شود.

1. مقدمه

بانک های خازن قدرت به طور گسترده ای برای بهبود ضریب توان در سیستم های قدرت استفاده می شوند. توان واحد نزدیک به واحد دارای چندین مزیت مانند کاهش تلفات در فیدرهای توزیع، افزایش ظرفیت خطوط انتقال برق و ترانسفورماتورها و همچنین مشخصات ولتاژ مورد نظر است. با توجه به تنوع مستمر از بارهای القائی در سیستم های قدرت، بانک های خازنی باید اغلب با یک رگولاتور ضریب قدرت اتوماتیک با توجه به ضریب قدرت مورد نیاز در پستها یا کارخانه های صنعتی روشن / خاموش شوند [1]. با این حال، اضافه ولتاژ گذرا و جریان هجومی در شرایط سوییچینگ خازن بوجود می آیند [2]. علاوه بر تنزل کیفیت قدرت، چنین موارد گذرا منجر به کاهش در طول عمر خازن و دستگاه سوئیچینگ می شود. بنابراین، برخی از استانداردها در مورد سوئیچینگ خازن توصیه شده است [3، 4]. علاوه بر این، چندین روش برای مهار حالات گذرای سوییچنگ خازن پیشنهاد شده است که به طور کلی بر اساس دو مفهوم است: افزایش امپدانس خط در سوییچینگ فوری و یا نزدیک به اتصالات سوئیچ هنگامی که ولتاژ در سراسر اتصالات صفر است. در [2]، یک راکتور سری محدودکننده جریان برای محدودکننده کردن موارد سوییچینگ خازن ارائه شده است. این روش, ساده و ارزان است، اما یک راکتور ثابت ممکن است سبب تشدید سیستم شود. بنابراین رتبه بندی ولتاژ افزایش یافته بانک خازنی ممکن است لازم باشد تا این تکنیک استفاده شود. مقاومت / سلف قبل از جاسازی, روش دیگری است، که در [5، 6] پیشنهاد شده است. سوئیچینگ ولتاژ-صفر اتصالات سوئیچ [7، 8] و تکنیک های مبتنی بر کنترل الکترونیکی قدرت [9/12] گزینه های دیگر می باشند. این روش ها به یک مدار کنترل اضافی نیاز دارند که منجر به افزایش در هزینه و پیچیدگی می شود. علاوه بر این، آنها کمتر قابل اعتماد هستند.

در این مقاله, یک محدودکننده گذرای سوییچینگ خازن حالت جامد کارآمد(SSCSTL) برای محدود کردن حالات گذرای سوییچینگ خازن پیشنهاد شده است. پس از سوئیچینگ، SSCSTL به حالت الغای گذرا می رود به طوری که یک راکتور DC, جریان هجومی سوئیچینگ را محدود می کند، اضافه ولتاژ و سوییچینگ گذرا با استفاده از یک وریستور بریده می شود. پس از انرژی زایی بانک خازنی, SSCSTL به حالت بای پس می رود و یک تریستور (TH) راکتور DCرا باس پس (کنارگذر) می کند. بنابراین SSCSTL به عنوان یک مسیر اتصال کوتاه عمل می کند. در نتیجه، SSCSTL هیچ تاثیری بر روی مدار در حالت پایدار ندارد. SSCSTL دارای زمان پاسخ سریع برای سوییچینگ بین حالات محدودکننده کردن و کنارگذر است که <20 میلی ثانیه است. از یک مدار ساده و قابل اعتماد تحریک-خودکار برای دادن انرژی به بانک خازنی استفاده می کند. به عنوان یک نتیجه از استفاده از یک راکتور نوع -DC، هیچ نگرانی در مورد رزونانس سری وجود ندارد. علاوه بر حذف حالات گذرای سوئیچینگ خازن،SSCSTL , جریان خطا در بانک خازنی را محدود می کند.

بقیه مقاله به شرح زیر سازماندهی شده است: در بخش 2، پیکربندی SSCSTL و اصول عملکرد آن ارائه شده است. بخش 3 توسعه تجزیه و تحلیل مدار محدودکننده ارائه شده است. در بخش 4، عملکرد SSCSTL با استفاده از برخی از شبیه سازی و نتایج تجربی ارزیابی شده است. در نهایت در بخش 5 نتایج این مقاله را ارائه می دهد.

2 . ساختار SSCSTL و اصل عملکرد آن

توپولوژی تک فاز SSCSTL برای نشان دادن اصل عمل آن در نظر گرفته شده است. با این حال، می توان آن را مستقیماً به یک ساختار سه فاز افزایش داد. در این بخش, ساختار محدودکننده گذرای سوییچنیگ خازن پیشنهادی ارائه شده است. علاوه بر این, وظایف بخش های مختلف SSCSTL معرفی شده است. نهایتاً, حالات عملیات SSCSTL بررسی خواهد شد.

2.1 ساختار SSCSTL

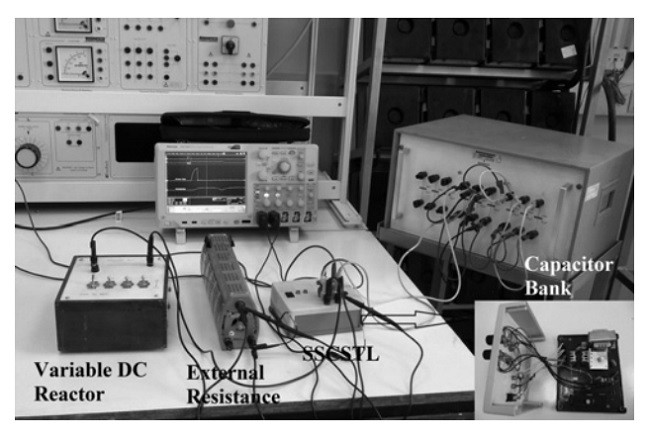

ساختار مدار SSCSTL در شکل.1 نشان داده شده است. ساختار آن را می توان به دو بخش تقسیم نمود: بخش قدرت و بخش کنترل. بخش قدرت از یک راکتور DC (L) ، یک مقاومت خارجی (RE)، یک یکسو کننده پل تک فاز و یا یکسو کننده قدرت (D1-D4)، یک Th و یک وریستور با قدرت بالا (MOV1) تشکیل شده است. بخش کنترل شامل یک ترانسفورماتور کم توان (T)، یک یکسو کننده تک فاز با ترانسفورماتور کم توان مرکز-شیر و یا یکسو کننده کنترل (Da و DB) و یک رگولاتور ولتاژ (L7805) می شود. راکتور DC به سمت DC یکسوکننده توان، به صورت اتصال موازی با Th، قطعات کمک فنر سری مقاومت-خازن (RC) (RS و CS) و یک مقاومت متغیر (MOV2) متصل می شود. به منظور جلوگیری از اشباع هسته در راکتور DC و کاهش شار باقی مانده، هسته سلف را می توان با یک شکاف هوا طراحی نمود. سلف, جریان هجومی سوییچینگ خازن را محدود می کند. قطعات وریستور (MOV2) و RC سری از Th در برابر سوئیچینگ اضافه ولتاژ گذرا حفاظت می کنند. ولتاژ بهره برداری از MOV2 بالاتر از حداکثر ولتاژ تغذیه انتخاب می شود. Th, سلف و قطعات کمک فنر را در شرایط حالت پایدار دور می زند. یک وریستور (MOV1) نیز برای حذف اضافه ولتاژ گذرای سوییچینگ خازن در نظر گرفته می شود. ولتاژ بهره برداری از MOV1 کمی بالاتر از ولتاژ بهره برداری MOV2 انتخاب می شود.

در بخش کنترل، یک ترانسفورماتور کم توان V 220/9 به صورت موازی با بانک خازنی متصل می شود. یک یکسو کننده تک فاز با ترانسفورماتور کم توان مرکز-شیر, مدار تحریک را تغذیه می کند. رگولاتور (L7805) برای محافظت از Th در برابر اضافه ولتاژ در کاتد گیت در نظر گرفته می شود.

2.2 اصل عمل SSCSTL

عوامل محدودکننده کننده ضروریSSCSTL پیشنهادی, یک راکتور DC/ وریستور MOV واقع شده به صورت سری / موازی با بانک خازنی هستند. اضافه ولتاژ گذرا در طی سوییچینگ توسط MOV حذف می شود. اضافه جریان گذرا توسط راکتور DC محدود می شود. بر این اساس، SSCSTL پیشنهادی دارای دو حالت عملیات است: حالت محدودکننده و حالت کنارگذر. در حالت محدودکننده (در لحظات اولیه بعد از سوییچینگ خازن)، ولتاژ خازن و ولتاژ ثانویهT کمتر از ولتاژ مورد نیاز برای هدایت Th هستند.

بنابراین، Th خاموش می ماند و راکتور DC و مقاومت خارجی, جریان هجومی بانک خازنی را محدود می کنند. علاوه بر این، اضافه ولتاژ گذرای سوییچینگ توسط وریستور MOV1 حذف می شود. در حالت بای پس (پس از ساخت ولتاژ مناسب در سراسر بانک خازنی)، ولتاژ ثانویه ترانسفورماتور T به یک سطح کافی می رسد که Th را روشن می کند و بنابراین راکتور DC کنارگذر خواهد شد. در واقع، جریان بانک خازنی از طریق Th و D1-D4 عبور می کند که به شکل مسیر اتصال کوتاه در می آید. یکسوساز مرکز-شیر و رگولاتور L7805 برای تحریک Th استفاده می شوند.

حالات محدودکننده و کنارگذر کردن SSCSTL پیشنهادی می تواند در دو حالت از عمل رده بندی شود که در بخش زیر توصیف شده است.

Abstract

Transient overvoltage and inrush current are two major transient phenomena which occur because of capacitor switching. In addition to power quality degradation, these transients lead to shortening the lifetime of the capacitor and switching device. In order to reduce these transients, a solid-state capacitor switching transient limiter (SSCSTL) is proposed in this study. The proposed SSCSTL has two operation modes: limiting mode and bypass mode. During the capacitor energising, a DC reactor and a varistor suppress inrush current and transient overvoltage, respectively. During the steady-state mode, the DC reactor is bypassed by a thyristor, so the SSCSTL acts as short-circuit and has no considerable effect on the circuit. The thyristor is triggered by using a new simple structure auto-triggering technique in normal condition. The proposed SSCSTL with a very simple structure as well as fast and reliable performance is an efficient solution to assure the capacitor switching without any transient overvoltage and inrush current. A prototype single-phase SSCSTL is simulated by electromagnetic transient program and tested. The simulation and experiment results show that the proposed SSCSTL considerably reduces the inrush current and transient overvoltage during switching of the capacitor.

1 Introduction

Power capacitor banks are widely used to improve the power factor in power systems. Closed to unity power factor has several advantages such as loss reduction in the distribution feeders, capacity increase of transmission lines and transformers, as well as the desired voltage profile. Owing to the continuous variation of the inductive loads in the power systems, capacitor banks should be switched on/off frequently by an automatic power factor regulator according to the required power factor in the substations or industrial plants [1]. However, transient overvoltage and inrush current arise in capacitor switching condition [2]. In addition to power quality degradation, such transients lead to a decrease in the lifetime of the capacitor and switching device. So, some standards have been recommended regarding the capacitor bank switching [3, 4]. Furthermore, several approaches have been proposed to restrain the capacitor switching transients, which are generally based on two concepts: increase the line impedance at the switching instant or close the switch contacts when the voltage across the contacts is zero. In [2], a series current limiting reactor is proposed to limit the capacitor switching transients. This method is simple and inexpensive, but a fixed reactor may cause system resonance. Therefore an increased voltage rating of the capacitor bank may be required when this technique is utilised. Pre-insertion resistor/inductor is another approach, suggested in [5, 6]. Zero-voltage switching of the switch contacts [7, 8] and power electronic control-based techniques [9–12] are other alternatives. These approaches require an additional control circuit, which leads to an increase in the cost and complexity. Furthermore, they are less reliable.

In this paper an efficient solid-state capacitor switching transient limiter (SSCSTL) is proposed for restriction of the capacitor switching transients. Upon switching, the SSCSTL goes to transient supersession mode so that a DC reactor limits the switching inrush current, and switching transient overvoltage is clamped by means of a varistor. After energisation of the capacitor bank, the SSCSTL goes to bypass mode and a thyristor (Th) bypasses the DC reactor, so the SSCSTL acts as a short-circuit path. Consequently, the SSCSTL has no effect on the circuit in steady state. The SSCSTL has a fast response time for switching between the limiting and bypass modes, which is <20 ms. It uses a simple and reliable auto-triggering circuit for energising the capacitor bank. As a result of the utilisation of a DC-type reactor, there is no concern about the series resonance. In addition to suppression of the capacitor switching transients, the SSCSTL limits the fault current in case of a fault occurrence in the capacitor bank.

The rest of the paper is organised as follows: in Section 2, configuration of the SSCSTL and its operation principles are presented. Section 3 develops the circuit analysis of the proposed limiter. In Section 4, performance of the SSCSTL is evaluated by using some simulation and experimental results. Finally, in Section 5 the results are concluded.

2 SSCSTL structure and its operation principle

A single-phase topology of the SSCSTL is considered to demonstrate its operation principle. However, it can be straightforwardly extended to a three-phase structure. In this section, the structure of the proposed capacitor switching transient limiter is presented. Furthermore, duties of different parts of the SSCSTL are introduced. Finally, the SSCSTL operation modes will be discussed.

2.1 SSCSTL structure

The circuit structure of the SSCSTL is shown in Fig. 1. Its structure can be divided into two sections: power section and control section. The power section is composed of a DC reactor (L), an external resistance (RE), a single-phase bridge rectifier or power rectifier (D1–D4), a Th and a high-power varistor (MOV1). The control section includes a low-power transformer (T), a single-phase rectifier with low-power centre-tap transformer or control rectifier (Da and Db), and a voltage regulator (L7805). The DC reactor is connected to the DC side of the power rectifier, connected in parallel with a Th, series resistor-capacitor (RC) snubber components (Rs and Cs) and a varistor (MOV2). In order to prevent core saturation in the DC reactor and reduce the remnant flux, the inductor core can be designed with an air gap. The inductor limits the inrush current of the capacitor switching. The varistor (MOV2) and series RC components protect the Th against transient overvoltage switching. Operation voltage of MOV2 is selected higher than the maximum of the supply voltage. The Th bypasses the inductor and snubber components in steady-state condition. A varistor (MOV1) is also considered for transient overvoltage suppression of the capacitor switching. Operation voltage of MOV1 is selected slightly higher than the operation voltage of MOV2.

In the control section, a low-power 220/9 V transformer is connected in parallel with the capacitor bank. A single-phase rectifier with low-power centre-tap transformer feeds the trigger circuit. The regulator (L7805) is considered to protect the Th against overvoltage in gate cathode.

2.2 SSCSTL operation principle

Essential limiting elements of the proposed SSCSTL are a DC reactor/MOV varistor placed in series/parallel with the capacitor bank, respectively. Transient overvoltage during switching is suppressed by the MOV. Transient overcurrent is limited by the DC reactor. Accordingly, the proposed SSCSTL has two operation modes: limiting mode and bypass mode. In the limiting mode (during initial moments after the capacitor switching), capacitor voltage and secondary voltage of T are less than the required voltage for driving the Th. So, Th remains off and the DC reactor and external resistor limit the inrush current of the capacitor bank. In addition, the switching transient overvoltage is suppressed by the varistor MOV1. In the bypass mode (after appropriate voltage build-up across the capacitor bank), secondary voltage of transformer T reaches a sufficient level, which turns-on the Th and so the DC reactor will be bypassed. In fact, the capacitor bank current passes through the Th and D1–D4, which forms a short-circuit path. The centre-tap rectifier and regulator L7805 are used for driving the Th.

The limiting and bypassing modes of the proposed SSCSTL can be categorised in two states of operation, which are described in the following section.

چکیده

1. مقدمه

2 . ساختار SSCSTL و اصل عملکرد آن

2.1 ساختار SSCSTL

2.2 اصل عمل SSCSTL

3 تحلیل و طراحی SSCSTL

3.1 تجزیه و تحلیل مدار

طراحی

4 شبیه سازی و نتایج تجربی

5 نتیجه گیری

Abstract

1 Introduction

2 SSCSTL structure and its operation

principle

2.1 SSCSTL structure

2.2 SSCSTL operation principle

3 Analysis and design of the SSCSTL

3.1 Circuit analysis

3.2 Design of the SSCSTL

4 Simulation and experimental results

5 Conclusion

6 References