دانلود رایگان مقاله یک SAR ADC، 20MS/s، 8 بیتی، منطقه کارآمد و توان پایین

چکیده

این مقاله نتایج طراحی نمونه اولیه بلوک IP یک مبدل آنالوگ به دیجیتال با تقریب متوالی (SAR ADC) را برای پیاده سازی با فن آوری 0.18 μm MMRF CMOS از شرکت UMC (تایوان) ارائه می دهد.

در درجه اول، واحد ADC در این مقاله با توجه به الزامات فنی بازخوانی دستگاه های الکترونیکی سیستم ردیابی سیلیکونی برای آزمایش ماده باریونی فشرده [Compressed Baryonic Matter] در دستگاه شتاب دهنده FAIR (www.gsi.de/en/research/fair.htm) طراحی شده است. هر چند، از این ADC می توان برای طیف وسیع تری از کاربردها هم استفاده کرد.

برای افزایش دقت و حصول اطمینان از قدرت تشخیص ADC از یک مقایسه کننده rail-to-rail استفاده شد. این ADC SAR بر روی تراشه ناحیه ای به مساحت 325 μm × 325 μm را اشغال می کند، ENOB برابر 6.88 بیت است، حداکثر DNL کمتر از 0.8 LSB و INL کمتر از 0.6 LSB است، فرکانس نمونه برداری 20 MHz، فرکانس ساعت 200 MHz و SNDR برابر 43.2 dB است. با این پارامترها ADC در ولتاژ تغذیه اسمی 1.8 V، در حدود 1.3 mA جریان مصرف می کند.

1. مقدمه

در ساختمان مدارهای مجتمع با کاربرد خاص (ASIC) برای سیستم های مختلف، آشکارساز بازخوانی اطلاعات یکی از بلوک های مهم مبدل های آنالوگ به دیجیتال (ADC) است. به طور خاص، ADC ها برای سیستم های داده - محور چند کانالی برای جمع آوری و پردازش داده ها با عملکرد غیر تصادفی سازی [derandomization] آنالوگ مورد نیاز هستند، که در [1]، [2] برای آزمایش CBM در مرکز شتاب دهنده بین المللی FAIR طراحی شده اند.

الزامات اصلی یک ADC برای این کاربرد عبارتند از: ناحیه کوچک اشغال شده روی تراشه، مصرف توان کم و سرعت متوســط (10 - 100 MS/s). به منظور برآوردن الزامات فنی برای دستگاه های الکترونیکی بازخوانی سیستم ردیابی سیلیکونی CBM، از معماری خط لوله ای [pipeline] و ADC با تقریب متوالی به عنوان محبوب ترین راه حل ها استفاده می شود [3]. در مقایسه این دو معماری از تعدادی از آثار مدرن [4-7]، به نظر می رسد، مبدل آنالوگ به دیجیتال با تقریب متوالی (SAR) نسبت به ADC خط لوله ای، به دلیل مصرف توان بیشتر و ناحیه بزرگتر بر روی تراشه با معماری ADC خط لوله ای، برای سرعت های نمونه برداری در محدوده متوسط برتر باشد[3].

در این مقاله ما طراحی SAR ADC در فرآیند0.18 μm CMOS را ارائه می دهیم که از DAC توزیع مجدد بار استفاده می کند، و برای دستیابی به دقت خوب، مصرف توان کم و اشغال ناحیه کوچک بر روی تراشه طراحی شده است. اگر چه، فن آوری های پیشرفته تر اجازه می دهند ADCها عملکرد بهتری داشته باشند [3]، انجمن FAIR از فن آوری UMC 0.18 μm به عنوان فن آوری استاندارد استفاده می کند.

به منظور برآوردن مشخصات مصرف توان، این ADC به جای DAC مبتنی بر مقاومت، از یک مبدل دیجیتال به آنالوگ (DAC) مبتنی بر الگوریتم توزیع مجدد بار استفاده می کند[8]. لازم به ذکر است، که این DAC، توزیع مجدد بار را برای یک آرایه خازنی فراهم می کند، و در مقایسه با مدار مبتنی بر آرایه مقاومتی، منجر به افزایش دقت و بیشتر شدن سطح تراشه می شود. برای کاهش مساحت اشغال شده توسط ADC، تصمیم گرفته شد که یک DAC یک طرفه با یک خازن ساخته شود تا اطمینان حاصل شود دقت مقایسه کننده عملکرد rail-to-rail [9] برای ورودی داشته باشد. به لطف این کار ADC پیشنهاد شده در این مقاله، با یک ورودی، دقت و قدرت تشخیص بالایی به دست می آورد.

بر اساس موارد فوق، این مقاله یک SAR ADC با سرعت نمونه برداری متوسط ارائه می دهد که از آرایش تقارن مرکز مشترک، مدار بازنشانی [reset] SAR و مقایسه کننده rail-to-rail بهره می برد. در نتیجه، ADC دارای توان کم بوده و ناحیه کوچکی از سطح تراشه را اشغال می کند.

2. معماری ADC

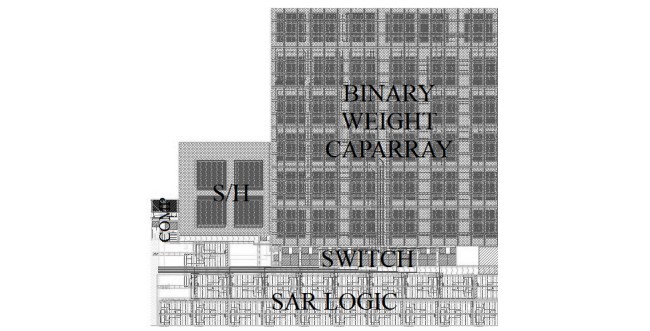

شکل 1 بلوک دیاگرام نمونه اولیه ساخته شده از مبدل آنالوگ به دیجیتال 8 بیتی را نشان می دهد که شامل یک مدار نمونه برداری و نگهدار (SH)، یک DAC، یک مقایسه کننده و بلوک کنترل SAR است.

A. چرخه ADC

چرخه عملیات ADC را می توان به مراحل زیر تقسیم کرد:

- در محل ورود سیگنال RST، بازنشانی ولتاژ ثبات تقریب متوالی و DAC وجود دارد.

- SH وارد فاز نمونه برداری می شود و شروع به ضبط سطح فعلی بار ورودی می کند.

- ثبات تقریب متوالی DAC MSB، که بزرگترین ظرفیت 128 Cunit را دارد، روشن می کند، DAC ولتاژی تولید می کند که برابر نصف مقیاس تبدیل کامل است.

- مقایسه کننده تصمیم می گیرد که در طول تبدیل MSB باید روی تنظیمات بالا و یا پایین [high or low] باقی بماند.

- مقایسه ادامه می یابد تا همه مقادیر بیت های خروجی تعیین شوند.

- پس از شناسایی همه 8 بیت، سیگنال پایان شمارش EOC تولید می شود، ADC تا زمان سیگنال بازنشانی بعدی RST مقدار خود را حفظ می کند.

B. مقایسه کننده

مقایسه کننده در شکل 2 نشان داده شده است. مقایسه دقیق سطح ولتاژ ورودی با ولتاژ ثابت شده توسط SHA که از DAC می آید، ضروری است. این مقایسه کننده دارای عملکرد rail-to-rail برای ورودی است تا دقت مورد نیاز را فراهم کند.

این مدارات با دو بخش مکمل موازی اجازه پوشش کل محدوده ولتاژ ورودی را می دهند. سیگنال های خروجی آن ها در یک مدار جمع کننده جریان، ترکیب شده و به ولتاژ تبدیل می شوند. بارهای طبقات ورودی دیفرانسیلی ترانزیستورهای متصل به دیود و تزویج متقابل هستند، که امپدانس خروجی بار طبقه اول مقایسه کننده را کاهش و بهره آن را افزایش می دهند [10]. خروجی های جریان طبقه اول به دیود (به عنوان یک ترانزیستور) که سیگنال جریان را به ولتاژ تبدیل می کند، و طبقه مقایسه کننده دوم، به یک منبع مشترک، تغذیه می شوند.

Abstract

This paper presents the design results of the prototype IP block of the successive approximation analog-todigital converter (SAR ADC) for implementation by 0.18 um MMRF CMOS technology of UMC (Taiwan).

Primarily the ADC unit was designed according to the technical requirements for the readout electronics of the silicon tracking system of the Compressed Baryonic Matter experiment at accelerator facility FAIR (www.gsi.de/en/research/fair.htm). However it can be used for a wider range of applications.

To increase accuracy and ensure ADC resolution a rail-torail comparator was used. The SAR ADC occupies on chip area of 325μm x 325μm, ENOB is 6.88 bits, maximum DNL less than 0.8 LSB, an INL less than 0.6 LSB, sampling frequency ‒ 20 MHz, clock frequency ‒ 200 MHz, and SNDR is 43.2 dB. With these parameters the ADC consumes about 1.3 mA at a nominal supply voltage of 1.8V.

I. INTRODUCTION

At building application-specific integrated circuits (ASIC) for different systems of detector data readout one of the important blocks is the analog-to-digital converter (ADC). In particular, ADCs are required for the multichannel data-driven system for collecting and processing data with the function of analogue derandomization, designed [1], [2] for the CBM experiment at the international accelerator facility FAIR.

The main requirements to an ADC for this application are: small area occupied on chip, low power consumption and medium speed (10-100 MS/s). In order to satisfy the technical requirements for the readout electronics of the CBM silicon tracking system, the pipeline architecture and successive approximation ADC are used as the most popular solutions [3]. At comparing these two architectures, from a number of modern works [4-7], the analog-to-digital converter with successive approximation (SAR) looks preferable against the pipelined ADC for the medium range of sampling rates, because of the greater power consumption and larger on chip area [3].

In this paper we present the design of SAR ADC in the 0.18μm CMOS process, which uses the charge redistribution DAC, designed to achieve good accuracy, low power consumption and the small area on chip. Although more advanced technologies allow the ADC to get a better performance [3], the UMC 0.18 μm used by FAIR community as standard.

In order to meet the specifications for power consumption, the ADC uses a digital-to-analog converter (DAC) based on the algorithm of charge-redistribution instead of the DAC based on resistors [8]. It should be noted, that the DAC provides a charge-redistribution for a capacitor array, resulting in an increased accuracy and more chip area, compared to the circuit based on the resistor array. To reduce the area occupied by the on-chip ADC it was decided to make a single ended DAC with one capacitor. To ensure accuracy comparator is made with the rail-to-rail [9] function for input. Thanks to this ADC, proposed in this paper, achieves high resolution and accuracy with one input.

Founded on the above points, this paper presents a moderate sample speed SAR ADC, which employs a common-centroid symmetry layout, SAR reset circuit and rail-to-rail comparator. As result, the ADC has a low power, and occupies a small area of chip.

II. ADC ARCHITECTURE

Fig. 1 shows a block diagram of the developed prototype of an 8-bit analog-to-digital converter, which contains a sample and hold circuit (SH), a DAC, a comparator and SAR control block.

A. ADC cycle

The operation cycle of the ADC can be divided into the following steps:

-on the arrival of the signal RST, there is reset the voltage of the successive approximation register and DAC.

-The SH enters the sampling phase and begins to record the current level of input charge.

-The successive-approximation-register turns on the DAC MSB, having the largest capacity of 128Cunit, the DAC forms a voltage, equal to a half the full transformation scale.

-The comparator decides if the MSB should remain high or set low during the conversion.

-Comparison continues until all the values of output bits are determined.

-After identifying all 8 bits, the signal of count finish EOC is generated, the ADC retains its value until the next reset signal RST.

B. Comparator

The comparator is shown in Fig. 2. It is necessary for an accurate comparison, of the input voltage level with the voltage, fixed by SHA coming from the DAC. It has the function of rail-to-rail for input to provide the required accuracy.

The circuits with two parallel complementary parts allow to cover the entire range of input voltages. Their output signals are combined in a current summing circuit and converted into voltage. Loads for the differential input stages are the diode-connected and cross-coupled transistors, which lower the output impedance of the load of the first stage of the comparator, as well as increase its gain [10]. The current outputs of the first stage are fed to the diode (as a transistor) that converts a current signal into a voltage, and a second comparator stage: a common source.

The power supply of the comparator uses selfbiasing reference with short-channel transistors [10].

The designed comparator at signal of 20 MHz consumes 300 uA at an average, its voltage gain is 65 dB at a unity gain frequency of 230 MHz, the maximum switching time is 3.75 ns.

چکیده

1. مقدمه

2. معماری ADC

A. چرخه ADC

B. مقایسه کننده

C. منطق SAR

D. DAC

3. نتایج شبیه سازی و آرایش

4. نتیجه گیری

منابع

Abstract

1. INTRODUCTION

2. ADC ARCHITECTURE

A. ADC cycle

B. Comparator

C. SAR logic

D. DAC

3. SIMULATION RESULTS AND LAYOUT

4. CONCLUSION

REFERENCES