دانلود رایگان مقاله یک SAR ADC لوله ای 12 بیتی، 210 MS/s، 5.3mW با یک تکنیک انتقال باقیمانده غیر فعال

چکیده

یک مبدل آنالوگ به دیجیتال 12 بیتی دوکاناله 210MS/s (ADC) که روی معماری تقریب متوالی لوله ای بکار برده شده ارائه می شود. ADC به 3 مرحله، با انتقال باقیمانده غیر فعال بین مراحل اول و دوم و تقویت باقیمانده فعال بین مراحل دوم و سوم افراز می شود. ADC 5.3 m W از یک منبع 1 ولتی مصرف کرده و به SNDR 63.48 دسی بل در یک ورودی 5MHZ و 60.1 دسی بل نزدیک نرخ نایکوییست دست می یابد.

مقدمه

تقاضا روی ADC های رزولوشن-بالا پر سرعت، کم توان با تعدد کاربردها افزایش یافته که این نیاز به پهنای باند سیگنال عریض تر می باشد. برای رعایت مشخصات، ADC های لوله ای معمولا برای سرعت عالی تر مورد استفاده قرار می گیرند. بعبارت دیگر، با کم کردن مقیاس فناوری های CMOS، SAR ADC ها جای ADC های لوله ای را گرفته اند، بخاطر کارایی توان فوق العاده ای که دارند. وای عملکرد SAR ADC ها محدود است به دلیل نویز مقایسه کننده و تبدیل چرخش بیتی سریالی.

این کار از یک معماری SAR خط لوله ای برای بهبود گذردهی و همچنین تخفیف و کاهش پیش نیاز طراحی مقایسه کننده استفاده می کند. برای حداقل کردن تعداد OP AMP خورنده توان در امتداد مسیر سیگنال، SAR ADC های لوله ای معمولی عموماً از یک طرح 2 مرحله ای استفاده می کنند که نیازمند فقط یک OP AMP برای تقویت باقیمانده می باشد. یک متد انتقال باقیمانده غیر فعال در این کار پیشنهاد می شود تا عمل لوله کاری شده از 2 به 3 مرحله بسط یابد در حالیکه کارایی توان حفظ می شود. در ضمن، سه مقایسه گر میان مراحل چرخش داده می شوند تا شرط طراحی افست (انحراف) راحت شود.

معماری و پیاده سازی مدار

شکل 1 معماری ADC پیشنهادی را نشان می دهد. ADC بصورت 3 مرحله پیکر بندی شده و هر مرحله 4 بیت، 5 بیت و 6 بیت را به ترتیب تفکیک می کند تا خروجی 12 بیتی تولید شود. یک بیت اضافی توسط مرحله آخر تفکیک می شود که برای کالیبراسیون بهره مورد استفاده قرار می گیرد.

در پایان مرحله اول تبدیل A/D، DAC باقیمانده متناظر را تولید می کند که بعد به صورت غیر فعال به مرحله دو منتقل می شود. یک آمپلی فایر باقیمانده 8x (RA) مشترک بین کانال ها بین مراحل دوم و سوم جای می گیرد تا نویز عقبه و نیازهای افست رفع شوند.

برای یک SAR ADC معمولی، خازن DAC (CDAC) همیشه دوباره تنظیم می شود وقتی که این تبدیل تمام می شود. اگر باز ذخیره شده روی CDAC بتواند دوباره استفاده شود توان قابل توجهی برای تولید باقیمانده می تواند ذخیره شود. ایده انتقال باقیمانده غیر فعال در شکل 2 نشان داده می شود.

با در نظر گرفتن یک SAR ADC 4 بیتی با نمونه برداری صفحه-زیرین معمولی بعنوان مرحله اول، نسبت خازن برای D/A باینری 8:4:2:1:1 نشان داده می شود. وقتی تبدیل انجام می شود، باقیمانده روی این خازن ها ذخیره می شود. پس یکی از خارن ها می تواند برای فرایند SAR بعدی به مرحله دوم برود. بعبارت دیگر، باقی خازن ها در مرحله اول، برای نمونه وارد شونده بعدی، نگهداری می شوند. در این طراحی، دو نیمه خازن MSB، ، برای انتقال باقیمانده مورد استفاده قرار می گیرند که الزام نویز KT/C را رعایت می کند. وقتی یک باقیمانده را از مرحله اول به دوم جابجا می کند، نوع دیگر متناظر با آن به عقب به مرحله اول سوئیچ می شود. این عمل پینگ پونگی، انتقال باقیمانده را بدون هر نوع مولفه فعال امکان پذیر می کند. همراه با سوئیچ ها از طریق متد پیشنهادی، ADC با خطای بهره ناشی از برق پذیری پارازیتی غیر خطی هنوز به حدود کارایی 13 بیتی مطابق با شبیه سازی دست می یابد. در ضمن، زمان ته نشانی DAC، گلوگاه سرعت اصلی در مرحله اول می شود؛ بخاطر برق پذیری نسبتا بزرگ آن. یک راهکار ساده این است که از خازن های افزونه و سیکل های تصمیم برای تحمل خطای ته نشانی DAC با جریمه برق پذیری ورودی مازاد و سربار محدوده پویا استفاده شود. برای تفکیک مسائل طراحی، طبق شکل 3، سه خازن MSB اول شکسته می شوند و یک سیکل اضافه برای پیاده سازی 2.8 بیتی در حین تبدیل 4 بیت در مرحله اول اضافه می شود، زیرا که خطاهای ته نشانی بزرگ معمولا در ابتدا و سوئیچینگ DAC ثانوی رخ می دهند. مشابه با مرحله 2.8 بیتی یک ADC موازی سازی شده، تحمل خطا، ±Vref/8 است. در این کار، طرح ته نشانی DAC ناکامل و نویز مقایسه گر محقق می شود.

Abstract

A 210 MS/s dual-channel 12-bit analog-to-digital converter (ADC) employing a pipelined successive approximation (SAR) architecture is presented. The ADC is partitioned into 3 stages with passive residue transferring between the 1st and the 2nd stages and active residue amplification between the 2nd and the 3rd stages. The ADC consumes 5.3 mW from a 1-V supply and achieves an SNDR of 63.48 dB at a 5-MHz input and 60.1 dB near Nyquist-rate.

Introduction

The demand on low-power, high-speed, and high-resolution ADCs has increased as many applications require wider signal bandwidth recently. To satisfy the specifications, pipelined ADCs [1] are typically used for their superior speed. On the other hand, with the scaling down of CMOS technologies, SAR ADCs have been replacing pipelined ADCs because of their excellent power efficiency. But the performance of SAR ADCs is limited due to comparator noise and the serial bit-cycling conversion.

This work employs a pipelined-SAR [2]-[4] architecture to enhance the throughput as well as to relax the design requirement of the comparator. To minimize the number of the power-hunger op amps along the signal path, conventional pipelined-SAR ADCs usually adopt a 2-stage scheme which requires only one op amp for residue amplification. A passive residue transferring method is proposed in this work to extend the pipelined operation from 2 to 3 stages while retaining the power efficiency. Besides, three comparators are rotated among the stages to ease the offset design constrain.

Architecture and Circuit Implementation

Fig. 1 shows the proposed ADC architecture. The ADC is configured as 3 stages and each stage resolves 4 bits, 5 bits, and 6 bits respectively to generate a 12-bit output. The extra one bit resolved by the last stage is used for the gain calibration.

At the end of 1st stage A/D conversion, the DAC generates the corresponding residue which then be transferred to the 2nd stage passively. An 8x residue amplifier (RA) shared between channels is placed between the 2nd and the 3rd stages to alleviate backend noise and offset requirements.

For a conventional SAR ADC, the capacitor-DAC (CDAC) is always reset when it finishes conversion. If the charge stored on the CDAC could be reused, considerable power for residue generation can be saved. The idea of passive residue transferring is illustrated in Fig. 2.

Considering a conventional bottom-plate sampling 4-bit SAR ADC as the 1st stage, the capacitor ratio for the binary D/A is 8:4:2:1:1 as shown. Once the conversion is done, the residue is stored on these capacitors. Thus, one of the capacitors could be moved to the 2nd stage for the following SAR process. On the other hand, the rest of capacitors are kept in the 1st stage for the next incoming sample. In this design, two half of the MSB capacitors, 4Cu1, are served for the residue transferring to meet the kT/C noise requirement. When one 4Cu1 moves the residue from the 1st to the 2nd stage, the other one is switched back to the 1st stage correspondingly. This ping-pong operation enables the residue transferring without any active components. Together with the switches via the proposed method, the ADC with the gain error induced by nonlinear parasitic capacitance still achieves about a 13-bit accuracy according to simulation. In addition, DAC settling time becomes the main speed bottleneck in the 1st stage because of the relatively large capacitance. A simple solution [5] employs redundant capacitors and decision cycles to tolerate DAC settling error with the penalty of the extra input capacitance and dynamic range overhead. To resolve the design issues, as shown in the Fig. 3, the first three MSB capacitors are split and an extra cycle is added for 2.8-bit implementation during the 4-bit conversion in the 1st stage, where large settling errors typically occur in the first and the second DAC switching. Similar to a 2.8-bit stage of a pipelined ADC, the error tolerance is ±Vref/8. In this work, the scheme accommodates the incomplete DAC settling and the comparator noise.

چکیده

مقدمه

معماری و پیاده سازی مدار

نتایج تجربی

منابع

Abstract

Introduction

Architecture and Circuit Implementation

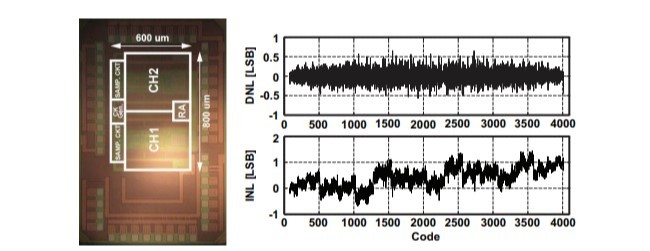

Experimental Results

References