دانلود رایگان مقاله گیرنده رادیویی پهن باند 65 nm CMOS با فیلترهای انتخاب کانال تبدیل کننده

چکیده

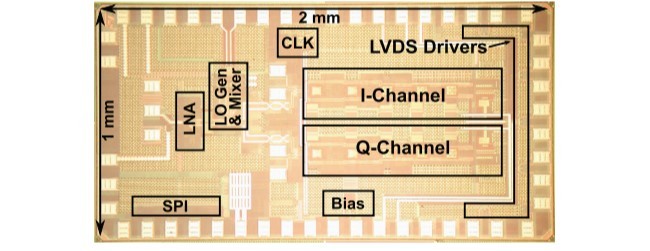

در این مقاله یک گیرنده رادیویی تربیعی پهن باند با به کارگیری فیلترهای انتخاب کانال تبدیل کننده A/D بر اساس مدولاسیون ΔΣ (ADCSF) ارائه شده است. خروجی میکسر پسیو تربیعی به طور مستقیم به ورودی ADCSF ها متصل می شود، که در آن یک مدولاتور مرتبه اول ΔΣ در یک فیلتر انتخاب کانال باترورث مرتبه چهارم (CSF) برای تأمین محدوده دینامیکی کافی برای سیستم سلولی گنجانیده شده است. در روش به دست آمده برای طراحی ADCSF تابع انتقال CSF حفظ می شود. گیرنده 65 nm CMOS دارای محدوده فرکانسی 0.6 - 3.0 GHz است و می تواند برای پشتیبانی از پهنای باندهای 2xLTE20، LTE20 و LTE10 برنامه ریزی شود. عدد نویز این گیرنده از 2.3 dB تا 3.9 dB تغییر است، مصرف جریان آن در حالت 2xLTE20 بین 3.3 mA در 0.6 GHz و 44 mA در 3.0 GHz بوده و از یک منبع 1.2 V تغذیه می کند که شامل 10 - 21 mA برای تولید و توزیع فاز LO است. مقدار SNDR در فرکانس GHz 1.8 LO، برابر با 47-51 dB است.

1. مقدمه

در گیرنده های رادیویی سلولی مدرن (RX) الزامات سختگیرانه، نه تنها در مورد پهنای باند، توان، و مصرف سطح، بلکه درباره رد مداخله گر تهاجمی مورد نیاز در استانداردهای ارتباطی مانند LTE نیز در حال افزایش است. شکل (a)1 معماری تبدیل مستقیم RX را نشان می دهد که در آن RF پیشرو در حالت جریانی کار می کند. تقویت کننده هدایت انتقالی نویز پایین (LNTA) تبدیل ولتاژ به جریان و تقویت آن را انجام می دهد، و جریان خروجی آن برای کاهش فرکانس به میکسر تربیعی پسیو تغــــذیه می شود. پس از آن، یک تقویت کننده امپدانس انتقالی (TIA) سیگنال حالت جریان را به حالت ولتاژ تبدیل کرده و آن را تقویت می کند. قبل از تبدیل نهایی به حوزه دیجیتال، فیلتر انتخاب کانال پایین گذر (CSF) به طور معمول مداخله گرها (هم نزدیک و هم دور) را تضعیف می کند، به طوری که شرط محدوده دینامیکی (DR) در مبدل آنالوگ به دیجیتال (ADC) تخفیف می یابد، و اجرای توان کارآمد RX را تضمین می کند. مدولاتور ΔΣ (DSM) زمان پیوسته (CT)، به علت مقاوم بودن آن نسبت به موارد غیره ایده آل بودن مدار و فیلترینگ ضمنی ضد پلگی [Anti- aliasing]، یک انتخاب مناسب برای RX ADC است [1].

در چند کار اخیر برای دستیابی به کاهش توان و سطح کل برای داشتن عملکردی مشابه با CSF و DSM کاسکاد استاندارد، CSF و DSM به صورت همزمان طراحی شده است. یک روش ممکن برای این کار جاسازی CSF در DSM است [2]، [3]، که باعث کاهش نویز و عملکرد خطی CSF می شود، در حالی که تابع انتقال نویز (NTF) DSM تحت تأثیر CSF جاسازی شده قرار نمی گیرد.

رویکرد دوم، که با پیشگامی Sosio و همکاران در [4]، [5] ارائه شد و در [6]، [7] بیشتر توسعه یافت، روش انتخاب شده در این کار است و می تواند به عنوان دوگان روش اول توصیف شود: DSM داخل حلقه فیدبک کلی CSF جاسازی شده است [نگاه کنید به شکل (b)1]، که دارای مزیت شکل دهی اضافی فرکانس نویز DSM به وسیله قطب های CSF است، در نتیجه شرایط نویز تدریج [quantization] و حرارتی در خود DSM تخفیف می یابد. علاوه بر این، با استفاده از مقدار نسبتاً کم بهره در اولین انتگرالگیر CSF، TIA را می توان در CSF گنجانید. بنابراین، CSF تبدیل کننده A/D (ADCSF) شکل (c)1 قابلیت های عملکردی TIA، CSF، و ADC را با هم ترکیب می کند، در همان زمان مصرف توان و (احتمالاً) سطح را بهبود می بخشد.

جاسازی ADC در داخل CSF شیفت فازهای اضافی اجتناب ناپذیر در مسیر سیگنال وارد می کند، که از عوامل زیر ناشــــی می شوند: 1) از تبدیل دیجیتال به آنالوگ (DAC) در مسیر فیدبک ADCSF و 2) از این واقعیت که در کل تابع انتقال سیگنال (STF) DSM برابر واحد نیست. چنین شیفت فازهایی مکان قطب های CSF را تغییر می دهند، و تنظیم دوباره ضرایب CSF برای بازیابی STF CSF مورد نظر ضروری است. یک روش طراحی با در نظر گرفتن تأخیرهای DSM DAC در [7] توسعه داده شده است. با این حال، در آن کار STF DSM هنوز هم واحد در نظر گرفته شده است، و این فرض برای DSMهای مرتبه پایین به واقعیت نزدیک تر است، که در نتیجه در زمینه طراحی ADCSF ترجیح داده می شود.

در این مقاله، که یک نسخه تعمیم یافته از مرجع [8] است، یک RX تک سر ارائه داده ایم که در آن یک LNTA پهن باند و پس از آن یک میکسر پسیو تربیعی حالت جریان به طور مستقیم به دو ADCSF یکسان، یکی برای هر مسیر I/Q وصل شده است. با توجه به ADC فیلترینگ ارائه شده در [7] ADCSF، STF این مقاله به علت استفاده از DSM مرتبه اول ساده تر (به جای مرتبه دوم) رفتار بهتری از خود نشان می دهد. هم چنین این STF گزینندگی فرکانس قوی تر، نسبت سیگنال به نویز و اعوجاج (SNDR) بالاتر ADCSF، و عدد شایستگی (FOM) بهتری دارد. در مقایسه با RXهای [9] - [11]، این RX به عدد نویز پایین تر، مصرف توان کمتر، و فیلترینگ تهاجمی تر برای تضعیف کانال های مجاور دست پیدا می کند.

این مقاله به شرح زیر سازمان دهی شده است. بخش II یک مرور کلی از طراحی RX ارائه می دهد و درباره نمودار خصوصیات مداخله گر (مسدود کننده) بحث می کند. استراتژی طراحی سنتز ADCSF در بخش III مورد بحث قرار گرفته، و پیاده سازی مدار RF پیشرو و ADCSF با جزئیات در بخش IV ارائه شده است، به دنبال آن نتایج اندازه گیری برای ADCSF مستقل (بخش V) و برای کل RX (بخش VI) آمده است. در نهایت، نتیجه گیری ها در بخش VII ارائه شده است.

2. بررسی اجمالی سیستم

هدف ما یک گیرنده پهن باند است که می تواند برای باندهای RF متعدد استفاده شود. این RX از رد هارمونیک استفاده نمی¬کند، چون که یک فیلتر آنتن (در حالت TDD) و یا یک دوپلکسر (در حالت FDD) برای رد سیگنال های خیلی خارج از باند (OOB) در هارمونیک های فرد fLO در نظر گرفته شده است. LNTA پهن باند تک سر به تفاضلی با هدایت انتقالی قابل تنظیم، با ارائه بهره متغیر، میکسر پسیو تربیعی حالت جریان را به کار می اندازد، همان طور که در شکل (c)1 نشان داده شده است. سپس، سیگنالی که فرکانس آن کاهش یافته توسط ADCSF ها پردازش شده، سیگنال تربیعی دیجیتال را برای پردازش بیشتر در باند پایه دیجیتال تحویل می دهد. همان طور که قبلاً بحث شد، ADCSF شامل قابلیت های عملکردی TIA، CSF و ADC است. ADCSF امپدانس انتقالی 10 kΩ فراهم می کند، و در نتیجه بهره ولتاژ اسمی کلی RX برابر 50 dB است که از ورودی LNTA به خروجی ADCSF تفاضلی محاسبه شده است. پهنای باند RX را می توان برای پشتیبانی LTE10، LTE20، یا دو کانال LTE20 که به صورت همجوار جمع شده اند (2xLTE20) پیکربندی کرد.

یکی از چالش های اصلی در طراحی RX سروکار داشتن با کانال مطلوب ضعیف در حضور مداخله گرهای قوی است. موارد آزمون نمونه تعریف شده توسط 3GPP [12] برای LTE20، با افست فرکانس foffset از فرکانس حامل، در شکل 2 نشان داده شده اند. حساسیت مرجع (REFSENS)، که اشاره به حداقل سطح توان سیگنال درون باند (IB) برای آشکارسازی در پورت آنتن دارد، ممکن است به کمی -94 dBm باشد. برای LTE، REFSENS مدولاسیون QPSK با نرخ کد ⅓ را در نظر می گیرد، که باعث می شود نسبت سیگنال به نویز (SNR) مورد نیاز برای %95 از حداکثر توان عملیاتی دست یافتنی -1 dB باشد[13]. حساسیت RX در دمای اتاق (300 K) به صورت زیر تعریف شده است [13]

Abstract

This paper presents a wideband quadrature radio receiver employing ΔΣ-based A/D-converting channel-select filters (ADCSFs). The output of the quadrature passive mixer is directly connected to the input of the ADCSFs, where a first-order ΔΣ modulator is incorporated into a fourth-order Butterworth channel-select filter (CSF) to provide sufficient dynamic range for a cellular system. A design methodology for the ADCSF is derived, where the transfer function of the CSF is preserved. The 65 nm CMOS receiver has a frequency range of 0.6–3.0 GHz and can be programmed to support the 2xLTE20, LTE20, and LTE10 bandwidths. The receiver noise figure varies from 2.3 to 3.9 dB, with a current consumption in 2xLTE20 mode between 33 mA at 0.6 GHz and 44 mA at 3.0 GHz from a 1.2 V supply, including 10–21 mA for LO phase generation and distribution. The SNDR is 47–51 dB at an LO frequency of 1.8 GHz.

I. INTRODUCTION

THE demanding requirements on the modern cellular radio receiver (RX) are increasing not only concerning bandwidth, power, and area consumption, but also the aggressive interferer rejection needed in communication standards such as LTE. Fig. 1(a) shows the architecture of a direct-conversion RX, where the RF front-end is operated in current mode. The low-noise transconductance amplifier (LNTA) performs voltage-to-current conversion and amplification, and its output current is fed to the passive quadrature mixer for frequency down-conversion. Thereafter, a transimpedance amplifier (TIA) boosts and converts the current-mode signal into voltage mode. Before final conversion into the digital domain, a low-pass channel-select filter (CSF) typically attenuates the interferers (both close-in and far-out), so that the dynamic range (DR) requirement on the analog-to-digital converter (ADC) is relaxed, ensuring a power-efficient implementation of the RX. A continuous-time (CT) ΔΣ modulator (DSM) is a favorable choice for the RX ADC, because of its robustness to circuit nonidealities and implicit anti-aliasing filtering [1].

Several recent works have targeted the codesign of CSF and DSM, to achieve an overall power and area reduction for the same functionality of the standard cascade of CSF and DSM. A possible approach is to embed the CSF within the DSM [2], [3], which relaxes the noise and linearity performance of the CSF, while the noise transfer function (NTF) of the DSM is unaffected by the embedded CSF.

A second approach, pioneered by Sosio et al. in [4], [5], and further developed in [6], [7], is the one adopted in this work and can be described as the dual of the first: the DSM is embedded inside the global feedback loop of the CSF [see Fig. 1(b)], with the advantage of an additional frequency shaping of the DSM noise by the CSF poles, thereby relaxing the quantization- and thermal-noise requirement on the DSM itself. Furthermore, by using a modest amount of gain in the first CSF integrator, the TIA can be incorporated into the CSF. Thus, the A/D-converting CSF (ADCSF) of Fig. 1(c) combines the functionalities of TIA, CSF, and ADC, improving at the same time power and (possibly) area consumption.

Embedding the ADC into the CSF introduces unavoidable extra phase shifts on the signal path, originating: 1) from the digital-to-analog conversion (DAC) in the feedback path of the ADCSF and 2) from the fact that the signal transfer function (STF) of the DSM is not equal to unity in general. Such phase shifts alter the CSF pole locations, and re-tuning of the CSF coefficients becomes necessary to restore the desired CSF STF. A design method accounting for DSM DAC delays has been developed in [7]. In that work, however, the DSM STF was still assumed to be unity, and this assumption is closer to reality for lower-order DSMs, which are therefore to be preferred in the context of ADCSF design.

In this paper, which is an extended version of [8], we present a single-ended RX where a wideband LNTA is followed by a current-mode quadrature passive mixer directly connected to two identical ADCSFs, one for each I/Q path. With respect to the filtering ADC presented in [7], the ADCSF in this paper exhibits a better behaved STF thanks to the use of a simpler first-order (instead of second-order) DSM. It also displays a stronger frequency selectivity, a higher ADCSF signal-to-noise-and-distortion ratio (SNDR), and a better figure-of-merit (FoM). Compared to the RXs in [9]–[11], this RX achieves a lower noise figure, lower power consumption, and more aggressive filtering to attenuate adjacent channels.

This paper is organized as follows. Section II presents an overview of the RX design and discusses the interferer (blocker) profile. The design strategy for ADCSF synthesis is discussed in Section III, and the circuit implementations of both RF frontend and ADCSF are detailed in Section IV, followed by the measurement results for the stand-alone ADCSF (Section V) and for the whole RX (Section VI). Finally, conclusions are drawn in Section VII.

II. SYSTEM OVERVIEW

We target a wideband receiver that can be used for multiple RF bands. The RX does not utilize harmonic rejection, since an antenna filter (in TDD mode) or a duplexer (in FDD mode) is assumed to reject far out-of-band (OOB) signals at the odd harmonics of fLO. A wideband single-ended-to-differential LNTA with tunable transconductance, providing variable gain, drives the quadrature current-mode passive mixer, as shown in Fig. 1(c). The down-converted signal is then processed by the ADCSFs, delivering the digital quadrature signal for further processing in the digital baseband. As already discussed, the ADCSF incorporates the functionalities of TIA, CSF, and ADC. The ADCSF provides a transimpedance of 10kΩ, resulting in a nominal overall RX voltage gain of 50 dB, calculated from LNTA input to differential ADCSF output. The RX bandwidth can be configured to support LTE10, LTE20, or two contiguously aggregated LTE20 channels (2xLTE20).

One of the main challenges in RX design is to handle the weak desired channel in the presence of strong interferers. Typical test cases defined by 3GPP [12] for LTE20 are shown in Fig. 2, with frequency offset foffset from the carrier frequency. The reference sensitivity (REFSENS), which refers to the minimum power level of the in-band (IB) signal to be detected at the antenna port, may be as low as −94 dBm. For LTE, REFSENS assumes a QPSK modulation with a code rate of 1/3, yielding a signal-to-noise ratio (SNR) requirement of approximately −1 dB for 95% of the maximum achievable throughput [13]. The RX sensitivity at room temperature (300 K) is defined as [13]

چکیده

1. مقدمه

2. بررسی اجمالی سیستم

3. ملاحظات طراحی ADCSF

A. RX SNR و ADC SQNR

B. مرتبه ADCSF در مقابل DSM

C. ADCSF در مقابل مرتبه و نوع CSF

D. گزینندگی در مقابل حساسیت

E. ADCSF در مقابل متعارف DSM

4. اجرای RX

A. RF پیشرو

B. باندپایه آنالوگ

C. جبران فرکانس OTA

5. نتایج اندازه گیری ACDF مستقل

6. نتایج اندازه گیری RX

منابع

Abstract

1. INTRODUCTION

2. SYSTEM OVERVIEW

3. ADCSF DESIGN CONSIDERATIONS

A. RX SNDR and ADCSF SQNR

B. ADCSF Versus DSM Order

C. ADCSF Versus Order and Type of CSF

D. Selectivity Versus Sensitivity

E. ADCSF Versus Conventional DSM

4. RX IMPLEMENTATION

A. RF Front-End

B. Analog Baseband

C. OTA Frequency Compensation

5. STAND-ALONE ADCSF MEASUREMENT RESULTS

6. RX MEASUREMENT RESULTS

REFERENCES